您好!

我正在开发电路板、我们正在尝试在 DP83826中进行设计。 我通常理解自举引脚的概念、以便在上电复位后进行快速配置/行为。

一般而言、我看到许多引脚都分配了内部上拉或下拉电阻器。

此外、每个自举特定引脚都分配了默认值。

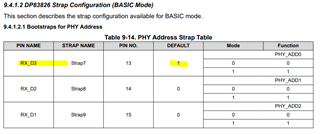

我希望确保了解默认值与每个引脚的指定 PU/PD 分配之间的关系。 在上面的示例中、在 基本模式下、该表指示 RX_D3/PHY_ADD0的默认值为 对我来说、这表示该引脚上存在内部上拉电阻。

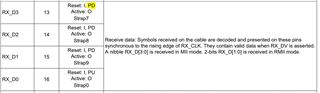

但是、当我查看数据表的表7-1时、该表指示为 RX_D3分配 了上电下拉电阻。 这向我表明、该引脚的"默认"值将为0、而不是表9-14中所示的1。

此外、我想澄清一下、在第9.4.1.2节中、如果列出的默认状态与我所需的芯片配置相匹配、 我 不需要添加任何外部上拉或下拉电阻器。 例如、表9-16表示默认行为是 启用了自动协商、因此、我不需要添加任何外部上拉/下拉?

不过、另一个示例是、我希望我的设计在启用全双工 的情况下退出复位、因此我需要在引脚16 (LED1/TX_ER)添加一个2.49k 下拉电阻、以便在上电时将模式注册为0 (全双工)。

感谢您对此提供的任何澄清。