主题中讨论的其他器件: DP83869

我们有一个用于新设计的电路板、但它在1G 时不通过 MII 环回。 某些消息通过 OK、但其他消息包含错误。 在错误消息中、我们观察到 RX 时钟从125MHz 增加到大约140MHz。 在正常消息中、RX 时钟保持在125MHz。 有什么想法可以导致这种情况? 是否有任何关于如何解决的建议?

我们在使用 DP83867的早期设计板和具有 DP83869HM 的其他项目板上运行了环回软件。 在这两种情况下、回送工作正常、没有错误。

谢谢、

Ron

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我们有一个用于新设计的电路板、但它在1G 时不通过 MII 环回。 某些消息通过 OK、但其他消息包含错误。 在错误消息中、我们观察到 RX 时钟从125MHz 增加到大约140MHz。 在正常消息中、RX 时钟保持在125MHz。 有什么想法可以导致这种情况? 是否有任何关于如何解决的建议?

我们在使用 DP83867的早期设计板和具有 DP83869HM 的其他项目板上运行了环回软件。 在这两种情况下、回送工作正常、没有错误。

谢谢、

Ron

Sreenivasa 您好、

我们最终能够使用晶体另一侧的负载电容器进行测试。 结果似乎是一样的,没有更好的,也没有更糟的。

在另一个 PHY 上、我们尝试了 FPGA 25MHz 输出上的电容分压器。 出于某种原因、现在 MII 总线上无法识别该 PHY。 我们将调查原因。 我猜可能是连接问题、或者是电容值导致输入过低。

在第三个 PHY 上、我们尝试将其强制为主器件、但它仍然作为从器件。 您是否会帮助确定我们应该写入寄存器的内容以强制其进入主模式? 以下是我们的软件工程师提供的信息:

配置为 MII 环回模式时、我查询 GEN_STATUS1 (0xA)寄存器的主/从状态(10/100/1000)。 在每种情况下,它都报告为“从属”。 我尝试在 Gen1_CFG1寄存器(0x9)上将其手动配置为主器件、但 GEN_Status1状态寄存器仍报告为从器件。 我不知道为什么设置不采用。 也许我们可以问 TI、我是否需要在初始化序列中执行不同的操作。 下面是我尝试将 PHY2配置为主器件回送时执行的寄存器读取/写入:

启动 PHY 自动协商(针对 DP83869HM 进行了修改-环回请求的最大速度1000)

GEN_CTRL 寄存器(0x001F)报告0x0000

GEN_CTRL 寄存器(0x001F)写入0x8000

BMCR 寄存器(0x0000)报告0x1140

BMCR 寄存器(0x0000)写入0x0140

RGMII_CTRL 寄存器(0x0032)写入0x00D0

BMCR 寄存器(0x0000)报告0x0140

BMCR 寄存器(0x0000)写入0x4140

Gen_CFG1寄存器(0x0009)报告0x0300

GEN_CFG1寄存器(0x0009)写入0x1B00

IO_MUX_CFG 寄存器(0x0170)报告0x0C10

IO_MUX_CFG 寄存器(0x0170)写入0x0C10

IO_MUX_CFG 寄存器(0x0170)报告0x0C10

GEN_CTRL 寄存器(0x001F)报告0x0000

GEN_CTRL 寄存器(0x001F)写入0x4000

GEN_STATUS1寄存器(0x000A)报告0x0000

phy 地址7的 MS_CONFIG_RES:从器件

报告0xA802的 PHY_STATUS 寄存器(0x0011)

PHY 地址7的链路模式:完全

Gem 0xFF0D0000配置为1000

您好 Ron、

早上好、感谢您的回复。

我看到 MII 环回已经在共享的寄存器中配置。 配置寄存器0x16应 将器件配置为主器件。

请尝试为下面的任何其他环回配置 PHY。

地址0x16 = 0x0004或0X0008

地址0x00 = 0x0140

地址0x1F = 0x4000

地址0x00FE = 0xE720

关于硬件更改、您是否将晶体位置移至负载电容器位置。 您是否希望将晶体移至更靠近 PHY 的位置并进行测试。 能否在 Xi 输入端添加一个100-200R 串联电阻器。

关于 FPGA 时钟-是时钟输出2.8V 或3.3V。 电容值随电压电平而变化。

是否有任何其他信号在靠近或靠近 Xi 的地方传递。 示例:对于867、MDC 引脚位于 Xi 引脚旁边。

此致、

Sreenivasa

您好、Sreenivasa、

感谢您的回答。 我们将尝试建议的寄存器值、以查看我们是否可以强制进入主模式。

在驱动 XI 的 FPGA 上、FPGA 的时钟输出为2.8V。 我们的伙伴们明天将在实验室中使用电容分压器电路探测和查看 Xi 信号的样子。 您是否有2.8V 输出的推荐值? Joe 转发给我们的文档中的单词"3.3V 时为27pF"、但2.8V 时不是推荐值。 我们的计划是分析信号以确定下一步要尝试的值。

对于晶体提供 Xi 的 PHY、我们没有重新定位晶体、只是移动了负载电容器。 我们的计划是串联安装一个电位计、以查看不同值的影响。 这样、我们就可以测试您建议的100-200欧姆。

我已要求我们的电路板布局工程师识别发送至 Xi 的任何附近信号。 我们在早期就了解了这一点,但没有发现任何令人关切的问题。

感谢您的支持、

Ron

您好 Ron、

感谢你的答复。

请注意、电容分压器与具有1.8V、2.5V 或3.3V IO 的 DP83867搭配使用、时钟范围始终为1.8V。

DP83869输入随 VDDIO 进行缩放。 以下主题可以提供帮助。

对于2.5V、建议的电容器值为 CD1=27pF 和 CD2=16pF。 对于3.3V 时钟、电容器值 CD1=CD2=27pF 正常。

下面是一篇文章、其中介绍了电容器值的解释和推导:

使用电位计检查是一个好主意。 挑战可能是电位计电阻分辨率。 必须考虑多转端口。

当您尝试使用硬件时、可能需要考虑晶体。

如果可能、您可以粉碎实际的晶体器件型号。 我可以在这里咨询设计团队、他们是否对使用过的晶体有任何想法。

对此,

Sreenivasa

您好、Sreenivasa、

感谢您的回答。 我们能够在我们的 PHY2上进行测试。 我们能够将 PHY2置于主模式并进行验证。 正如您所建议的、我们必须使用不同的回送模式、而不是 MII 回送。 相同的回送错误仍然存在。 这是否意味着不良的晶体源或不良的 PLL 或布局中其他信号的干扰?

您好、Sreenivasa、

在 PHY1上、FPGA 驱动 XI 输入、添加电容分压时发现接线错误。 我们修复了 PHY1再次正常工作、但错误相同。 尽管 XI 的时钟处于建议的工作范围内、但之前在 UDP 测试中看到的错误仍然可见(即100MHz 时没有自动协商)、这似乎违背了 FPGA 时钟过载 Xi 输入并导致双时钟和/或时钟错误的想法。 我们有示波器捕获、如果需要、我可以发送。 这是我们在路径上的工作、直到我们找到晶体振荡器不工作的根本原因。 我们是否应该像使用 PHY2 (晶体驱动 XI 的位置)那样在此上尝试回送? 是否有任何关于我们如何向前迈进的建议?

谢谢、

Ron

您好 Ron、

感谢您的更新。

您能不能帮助我了解您是否尝试过数字和模拟回路。

在 CLK_OUT = 25MHz 内部 PHY 参考时钟(0xCXX)的构建显示 、在错误消息期间、RX_CLK 仍增加到>140MHz、但 CLK_OUT 保持在25±0.2MHz。

您能否确认 在通信期间是否观察到此频率变化。

当您不进行通信时、您是否仍然看到频率 稳定。

您能否 检查 TX_ER 引脚是否靠近 Xi 布线? 是否可以 禁用 MAC 侧的 TX_ER 进行测试。 是否有任何其他 RGMII 信号在振荡器附近运行?

此致、

Sreenivasa

您好 Ron、

感谢您的回复。

您测量的晶体频率是多少。 您能否检查25MHz 的时钟输出是否看起来稳定。

当应用一个外部时钟时、如果在时钟稳定前释放复位、则可能会出现一些性能问题。

请查看 图4。 上电时序、并确认时钟稳定200ms 后复位释放。

您能否为125MHz 发送器时钟输出配置时钟输出并进行检查?

您是否有内部工具来生成和接收数据包以执行0x8 =反向环回

此致、

Sreenivasa

您好、Sreenivasa、

用蓝色回答 您的问题:

您能不能帮助我了解您是否尝试过数字和模拟回路。 他使用数字环回技术进行跑步、计划稍后运行模拟环回技术、但可能会在今年的第一年之后进行。 这是在 PHY2上、我们仍然有一个晶体驱动 Xi。 我们还想知道这是否意味 着不良的晶体源或不良的 PLL 或布局中其他信号的干扰?

在 CLK_OUT = 25MHz 内部 PHY 参考时钟(0xCXX)的构建显示 、在错误消息期间、RX_CLK 仍增加到>140MHz、但 CLK_OUT 保持在25±0.2MHz。

您能否确认 在通信期间是否观察到此频率变化。 这仅在发生不良传输时进行通信。 我们认为频率变化会导致传输不良。 我们将实现70-80%的良好通信、频率不变。 当我们能够在不良传输时触发时、我们观察到频率变化。 我曾尝试上传一个捕获、但网站不允许。

当您不进行通信时、您是否仍然看到频率 稳定。 当没有通信发生时、频率保持稳定。 在良好的通信过程中、它也是稳定的。

您能否 检查 TX_ER 引脚是否靠近 Xi 布线? 是否可以 禁用 MAC 侧的 TX_ER 进行测试。 是否有任何其他 RGMII 信号在振荡器附近运行? 在通信期间、我被告知此引脚未激活。 我已申请了西安附近的其他布线清单、但可能是在第一年之后才可以提供。 早在沟通开始之前、我们就仔细研究了这些其他迹线、这些迹线上的活动也发生在通信开始之前

您好、Sreenivasa、

以蓝色提供您的问题答案。 这与我们的 PHY1相关、FPGA 为 Xi 提供时钟:

您测量的晶体频率是多少。 您能否检查25MHz 的时钟输出是否看起来稳定。 是的、它是稳定的并且 CLK_OUT 是稳定的。 我无法上传文件、但下面是屏幕中的一个截点:

当应用一个外部时钟时、如果在时钟稳定前释放复位、则可能会出现一些性能问题。

请查看 图4。 上电时序、并确认时钟稳定200ms 后复位释放。 在使用 FPGA 进行驱动时、我们不满足此要求、但是、在 FPGA 时钟稳定后、我们通过软件命令进行复位。 我了解到软件复位命令与硬件复位具有相同的功能。 这是真的吗? 实验室中的人员执行了快速测试、在系统运行后、我们在软件配置 PHY 之前有60秒的延迟。 在此期间、通过短接线手动复位 RESET 引脚。 通过该测试、我们没有看到差异。

您能否为125MHz 发送器时钟输出配置时钟输出并进行检查? 我们可以,但不能确定这是昨天完成的。 我在示波器捕获中看不到它。 我们可能在第一年之后才能够收集这一数据。

您是否有内部工具来生成和接收数据包以执行0x8 =反向回送 请澄清运行此测试所需的条件。 是否可以通过连接到电路板的 PC 来完成此操作? 如果是、我们在 PC 上执行什么操作来实现这一点? 我们的另一个选择是引入867板。 您是否有我们可以用来运行此测试的任何测试软件?

谢谢、

Ron

您好、Sreenivasa、

在回答您的问题"您是否有机会在 Xi 和 X0上使用串联电阻器执行测试。 在振荡器电路周围有一些干扰的情况下、这将有助于实现这一目的。":

是的、我们确实做到了。 以下是乍得的说明:

当 POT 为0Ω Ω 时、捕获到 Xi 的信号并将其另存为示波器上的 R3参考波形(2.96Vpp、2.5V 高电平、捕获时的白色波形)。 在监测 XO 和 Xi 的情况下、POT 会旋转、直到 Xi 在 VDDIO=1.8V (设置为1.7Vpp、0.1-1.8V)的情况下看起来与 Xi 的首选输入范围相匹配。 电位计为200Ω μ F。 函数发生器与测试所需的 PHY0断开连接,但当发生器重新连接到 PHY0时,PHY3 XO 和 XI 信号的形状和振幅都显著下降(与启用/禁用函数发生器的输出一致)。 移动发生器的接地位置并将连接推离 PHY3测试区,我们能够使 PHY3上的时钟再次看起来干净,但 XI 振幅低于以前的值(XO 和以前一样)。 电位计再次旋转、直到 Xi 与 VDDIO=1.8V 的首选输入范围相匹配、此时电位计的电压为25Ω μ A。 PHY3通过管理总线进行通信(晶振功能)、但使用交换机内联在 PC (1000或10MHz)上未接收到数据。 交换机被移除、数据通过直接连接在 PC 上接收、但有效率较差(50%)

总之、串联电阻似乎没有产生影响、

Ron

嗨 、Sreenivasa、

问题解答。 在 PHY 的初始化或配置阶段、我们是否应该在以下引脚上看到任何活动?

CLK_OUT

RX_CNTL (38)

RX_CLK (32)

RX_D0 (33)

RX_D1 (34)

RX_D2 (35)

RX_D3 (36)

TX_CNTL (37)

TX_CLK (29)

TX_D0 (28)

TX_D1 (27)

TX_D2 (26)

TX_D3 (25)

"是/否"答案是可以的。 我们可以看到 SoC 编程期间发生了什么情况。 它们是否处于高阻态、我们是否会看到串扰。 无论怎样、我们都观察到一些活动、可能需要深入研究一些活动、除非这是 PHY 的预期行为。

希望您能在圣诞节/新年假期休息一下。 今天是我们1月4日星期二返回的最后一天。 希望您能与家人和朋友共度美好时光。 我们真的很期待这件事。

谢谢、

Ron

Ron 和 Chad、您好!

感谢您的详细输入。

您能否确认串行电阻器在与晶振一起运行的 PHY 上发生了变化? 我们需要将串联电阻添加到 PHY 的 XI 和 XO 输入或晶体输出端。

当 POT 为0Ω Ω 时、捕获到 Xi 的信号并将其另存为示波器上的 R3参考波形(2.96Vpp、2.5V 高电平、捕获时的白色波形)。

在监测 XO 和 Xi 的情况下、POT 会旋转、直到 Xi 在 VDDIO=1.8V (设置为1.7Vpp、0.1-1.8V)的情况下看起来与 Xi 的首选输入范围相匹配。 电位计为200Ω μ F。

函数发生 器与测试所需的 PHY0断开连接,但当发生器重新连接到 PHY0时,PHY3 XO 和 XI 信号的形状和振幅都显著下降(与启用/禁用函数发生器的输出一致)。

移动发生器的接地位置并将连接推离 PHY3测试区,我们能够使 PHY3上的时钟再次看起来干净,但 XI 振幅低于 以前的值(XO 和以前一样)。 电位计再次旋转、直到 Xi 与 VDDIO=1.8V 的首选输入范围相匹配、此时电位计的电压为25Ω μ A。

PHY3通过管理总线进行通信(晶振功能)、但使用交换机内联在 PC (1000或10MHz)上未接收到数据。

交换机被移除、数据通过直接连接在 PC 上接收、但有效率较差(50%)

此致、

Sreenivasa

您好、Sreenivasa、

以蓝色提供您的问题答案。 这与我们的 PHY1相关、FPGA 为 Xi 提供时钟:

您测量的晶体频率是多少。 您能否检查25MHz 的时钟输出是否看起来稳定。 是的、它是稳定的并且 CLK_OUT 是稳定的。 我无法上传文件、但下面是屏幕中的一个截点:

我是否可以要求您确认时钟频率是否在25MHz 的50-100 PPM 以内

当应用一个外部时钟时、如果在时钟稳定前释放复位、则可能会出现一些性能问题。

请查看 图4。 上电时序、并确认时钟稳定200ms 后复位释放。

在使用 FPGA 进行驱动时、我们不满足此要求、但是、在 FPGA 时钟稳定后、我们通过软件命令进行复位。 我了解到软件复位命令与硬件复位具有相同的功能。 这是真的吗? 实验室中的人员执行了快速测试、在系统运行后、我们在软件配置 PHY 之前有60秒的延迟。 在此期间、通过短接线手动复位 RESET 引脚。 通过该测试、我们没有看到差异。

遵循两个电源序列图、 时钟和上电时序(图4。 加电时序)是器件正常运行的重要要求。

如果在时钟稳定前复位有效、 使器件正常工作的唯一方法是引脚复位。 我看到一个来自 MAC 的 ENET1_RESET_N 引脚。

建议的顺序为图5。 复位时序。

不确定您是否有机会使用晶体在 PHY 上进行类似测量。 这是我们想要捕获的内容。

此致、

Sreenivasa

您好 Ron、

问题解答。 在 PHY 的初始化或配置阶段、我们是否应该在以下引脚上看到任何活动?

假设器件超出复位范围、电源稳定、此处显示了状态

CLK_OUT -将具有晶体输出。

从 PHY 传输到 MAC。

我希望时钟出现。 其他信号活动取决于来自铜接口的信号。

RX_CNTL (38)

RX_CLK (32)

RX_D0 (33)

RX_D1 (34)

RX_D2 (35)

RX_D3 (36)

从 MAC 到 PHY 的信号-可能是时钟输出可用。

TX_CNTL (37)

TX_CLK (29)

TX_D0 (28)

TX_D1 (27)

TX_D2 (26)

TX_D3 (25)

"是/否"答案是可以的。

信号已分类为答案。

此致、

Sreenivasa

您好 Ron、

对于晶体提供 Xi 的 PHY、我们没有重新定位晶体、只是移动了负载电容器。 我们的计划是串联安装一个电位计、以查看不同值的影响。 这样、我们就可以测试您建议的100-200欧姆。

我已要求我们的电路板布局工程师识别发送至 Xi 的任何附近信号。 我们在早期就了解了这一点,但没有发现任何令人关切的问题。

我假设您焊接了导线来连接函数发生器。 单独 的导线加上 函数发生器的驱动能力可能会有所帮助。

此外、我假设在 PHY 上电之前函数发生器已打开。 这会使时钟在释放复位之前保持稳定。

此致、

Sreenivasa

Sreenivasa 您好、新年快乐!

我们尚未找到 EVM、您是否会提供器件型号? 我今天早上向 Joe 发送了一封电子邮件、要求提供相同的信息。 此外、什么是"launchpad"? 这只是软件还是硬件? 我还需要一个器件型号。

我们正在进行修改、以允许 FPGA 在 FPGA 提供时钟时控制 PHY 复位、我们计划在今天晚些时候进行测试。 完成后将让您了解结果。

谢谢、

Ron

您好 Ron、

祝您 在2022年新年快乐。

感谢您的回复和更新计划。 Joe 也对这一问题采取了后续行动。

请参阅以下内容。 一个是 EVM

https://www.ti.com/tool/DP83869EVM

如果 MDIO 接口可访问、则 launchpad 是用于访问客户电路板上的 MDIO 寄存器的编程器。

https://www.ti.com/tool/MSP-EXP430F5529LP

此致、

Sreenivasa

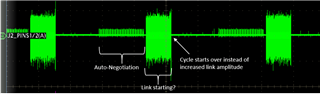

您好、Sreenivasa、

我们已经订购了 EVM 和编程器、仍在等待它到达。 同时,我们继续用 O’s 扫描进行故障排除。 我们从 FPGA 添加了一条复位线路、以保持 PHY 处于复位状态、直到 FPGA 的时钟稳定。 它现在符合数据表中的时序要求、但当 FPGA 提供 XI 输入时、PHY 仍然不能在1G 工作、但在使用函数发生器时工作。 我们已经尝试过带电容分压器和不带电容分压器的、但在使用 FPGA 时仍然无法正常工作。 当使用 FPGA 提供 XI 时、我们认为它没有完成自动协商、但仔细看、自动协商已完成、但链路未建立。 我们预计振幅会增加、但它会执行另一个自协商。 下面是 PHY 上的引脚1/2、其中 FPGA 位于 XI 上:

相比之下、当函数发生器用于 XI 时、链路开始工作时、幅值会增加:

是否有任何关于可能导致这种情况的想法?

谢谢、

Ron

Sreenivasa 您好、

我正在尝试再次上传文件、但另一天它将无法正常工作。

这是对 PHY0上的函数发生器 与 PHY1上的 FPGA 的比较。 这两个引脚都接入 PHY 的 XI 引脚。 我们最后做的一件事是将 PHY1重新接线以在 XI 上使用函数发生器 这确认了 PHY0和 PHY1与提供 XI 输入的函数发生器一起工作。

振幅差异可能是由于我在屏幕上执行了一个点按、然后上载。 我将会看到我现在是否可以上传文件、系统会提前让我上传。

Ron

您好、Sreenivasa、

以上问题的答案:

是两个波形使用的相同刻度。 链路脉冲振幅不会变化。 否 这就是为什么我提供了两个额外的波形、它们处于相同的刻度。

使用的链接伙伴(其他设备)是什么。 您能不能比较两个板的时钟。 这将是 Cisco 交换机。 因此、如果不拆解开关、就无法比较时钟。 看起来没有价值、因为我们看到交换机端口与其他 PHY 以及相同的 PHY 一起工作正常、但与功能生成时钟一起工作。

您能否比较函数发生器波形与 FPGA 波形形状和频率? 提供

请考虑使用电阻分压器进行测试、而不是使用电容分压器进行 FPGA 时钟分频。 当然、我们会将其添加到我们的列表中以尝试。

在 FPGA 生成的时钟上、我看到了一个步骤。 不确定这是由 FPGA 端口输出类型还是电容分压器导致的。

是否有方法可以检查它。 前置和后置电容分频器时钟捕捉:

我们可以尝试使用 RC 来消除干扰。 当您指出毛刺脉冲时、是不是过冲?

时钟规格对 MDI 接口有影响。

您是否拥有25MHz 振荡器? 我们的架子上没有一个。 我们在板上找到了一个要尝试挽救的板、不确定它是否起作用。

此致、

Ron

您好 Ron、

感谢您提供以下图表。 波形看起来不错、但振幅看起来更小。 我们将需要一个1.7V 的时钟。

方法一是调节电容器以获得所需的振幅。

第二种方法是使用电阻分压器对3.3V 进行分压。

振幅的变化有望得到解决。

是否有方法可以检查它。 前置和后置电容分频器时钟捕捉:

我们可以尝试使用 RC 来消除干扰。 当您指出毛刺脉冲时、是不是过冲?

时钟规格对 MDI 接口有影响。

您是否拥有25MHz 振荡器? 我们的架子上没有一个。 我们在板上找到了一个要尝试挽救的板、不确定它是否起作用。

此致、

Sreenivasa

您好、Sreenivasa、

是的、我可以再次发布。

关于在时钟稳定之前保持复位、我们进行了快速测试、在释放复位和 PHY 工作之前通电时禁用函数发生器输出、因此我们不认为在通电时没有时钟是问题所在。

关于您的建议:“您是否能够对 Xi 输入时钟和时钟输出执行时钟质量分析(抖动、相位噪声)。 请对 FPGA 的时钟输出和函数发生器执行相同的操作。"。 遗憾 的是、我们在实验中使用的信号分析器(Agilent N9010A exa X 系列)未安装相位噪声封装、但无论如何都能获得一些数据。 两个源极相似、迹线中没有可见抖动或相位调制。 这两个时钟之间的最大明显区别是 SOC 时钟稳定运行在24.9567MHz、而函数发生器稳定运行在25.0000MHz。 这可能是我们的问题。

我们仍然不明白为什么它不能像最初设计的那样与晶体一起工作。

您好 Ron、

感谢您的参与。

PHY 可以承受大约100PPM 的频率变化。 该容差看起来大约为1700PPM。

在使用板晶振时、我必须穿过已完成的路线。 我们讨论的其中一个问题是添加串联电阻器以及相邻信号对时钟的影响。

测试这种情况的一种方法是提供一个振荡器(类似于 EVM 上的振荡 器)、并将其连接到更靠近振荡器的位置。

您是不是偶然收到 EVM 的。 我们可以点击振荡器的时钟输出来进行快速测试。

此致、

Sreenivasa