https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1132994/tlk10232-sync-status

器件型号:TLK10232您好!

我们将 tlk10232作为双 SFI 应用的 phy 进行签名。 一个 SFI 通道与 SFP+ 10GBASE-SR 编译器连接、另一个通道与扩展范围 SFP+(10GBASE-ZR、80km)连接。 XAUI 两侧均连接到 Xilinx FPGA。 到目前为止、FPGA 设计仅控制从一个接口到另一个接口的传入流量。 XAUI IP 由 Xilinx 提供。

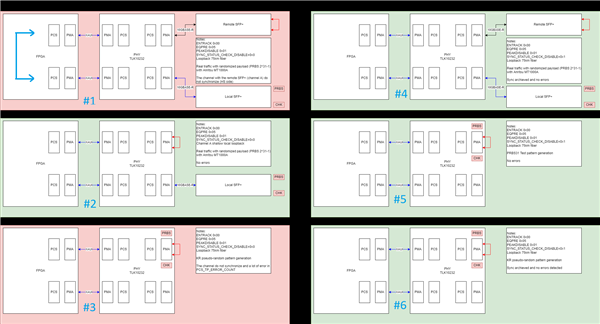

我们的测试装置包括一个通过短光纤链路连接到 SFP+基站 SR 的 Anritsu MT1000A 以太网测试仪、以及另一个 SFP+中75 km 的长光纤环回。 测试仪产生有效的以太网组帧、并且仅随机生成 有效载荷。 THA 为:测试仪 PRBS gen -> SFP+-> TLK10232.B -> FPGA -> TLK10232.A -> SFP+-> 75km 光纤环回-> SFP+-> TLK10232.A -> FPGA -> TLK10232.B -> SFP+->测试仪 PRBS 校验器。

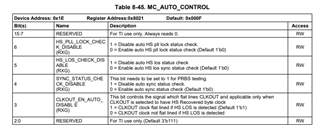

我们在10G-KR 中配置了 TLK10232 (禁用自动协商和链路协商),并且,正如差动文章和应用手册所述,HS_ENTRACK (0x1E.0004位15)配置为1'B1,HS_EQPRE (0x1E.0004位14:12)配置为3'B101。 在这种设置下、我们看到在通道 A (采用光纤环回的通道)中从未进行过重编程(0x1E.0010)和同步(0x1E000F 位10始终为1'b0)的错误。

在对 HS 侧的 RX 执行密集测试程序后、我们得出结论:HS_PEAKDISABLE (0x1E0004位6)至1'B1、HS_ENTRACK 至1'b0、HS_EQPRE 至3'B101是更好的配置。 正如其他博文和 TLK10xxx 高速串行器/解串器概述 所指出的、这也是10G 应用中的可靠配置。

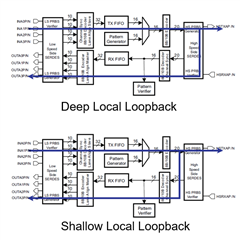

在这种配置下、错误消失了、但我们仍然有恒定的同步。 即使链路启动、如果我们打开光纤并再次关闭、通道也无法同步。

配置 HS RX 后、我们重点介绍了 TX。 使用环回、我们设置了 PRBS31测试模式生成和验证、如 TLK10232启动过程 所述。 测试完成后、我们可以看到、TWPRE、TWCRF、TWPOST1 y TWPOST2和 HS_Swing 的默认值设置为660mV、我们处于广域 OS 自由错误配置的中心。 但是、同步问题仍然存在。

此时、我们意识 到、尽管 SLLA351A 已说明、启动过程也会将伪 KR 随机测试模式的位 SYNC_STATUS_CHECK_DISABLE (0x1E.8021位4)设置为1'B1。 此模式将随机序列包装在有效的64/66B 块中、因此不应置位此位。

重点是、如果我们在正常操作中将 SYNC_STATUS_CHECK_DISABLE 设置为1'B1、同步问题似乎消失了、所有设计都正常工作。 问题是:SYNC_STATUS_CHECK_DISABLE 到底有什么作用? 和... SYNC_STATUS_CHECK_DISABLE = 1是否是有效的"生产"设置?

此致、

Daniel。