您好!

我们已经看到高电流消耗(大约30mA)、而 Enable'(低电平有效)引脚保持高电平、使能( 高电平有效)引脚保持高电平。 但是、当使能引脚保持低电平(而使能引脚仍保持高电平)时 、电流消耗降至19mA。 您能否解释一下在这种情况下电流消耗为何会越来越高?

| 引脚 | 状态 | 电流消耗(@VCC) |

使能 |

0 | 19mA |

| 使能 | 1 |

| 引脚 | 状态 | 电流消耗(@VCC) |

使能 |

1 | 30mA |

| 使能 | 1 |

此致、

Zafer Çalışkan è s

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们已经看到高电流消耗(大约30mA)、而 Enable'(低电平有效)引脚保持高电平、使能( 高电平有效)引脚保持高电平。 但是、当使能引脚保持低电平(而使能引脚仍保持高电平)时 、电流消耗降至19mA。 您能否解释一下在这种情况下电流消耗为何会越来越高?

| 引脚 | 状态 | 电流消耗(@VCC) |

使能 |

0 | 19mA |

| 使能 | 1 |

| 引脚 | 状态 | 电流消耗(@VCC) |

使能 |

1 | 30mA |

| 使能 | 1 |

此致、

Zafer Çalışkan è s

您好、Zafer、

您能否发送器件顶部的图片-我认为除了器件型号本身之外、还应该有更多的标记。

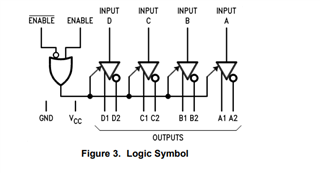

此外、对于真值表-没有显式表-但可以在功能方框图或逻辑符号的数据表中找到它:

/enable 和 enable 是或在一起的-因此真值表如下所示:

| 使能 | /enable | output_State |

| 1 | X | 使能 |

| X | 0 | 使能 |

| 0 | 1 | 禁用(高阻态) |

请告诉我器件的其他标记、以便我可以查看是否可以跟踪器件型号以检查其是否有效。

最棒的

Parker Dodson

谢谢 Zafer、

器件型号和标记看起来不错-因此这很好。

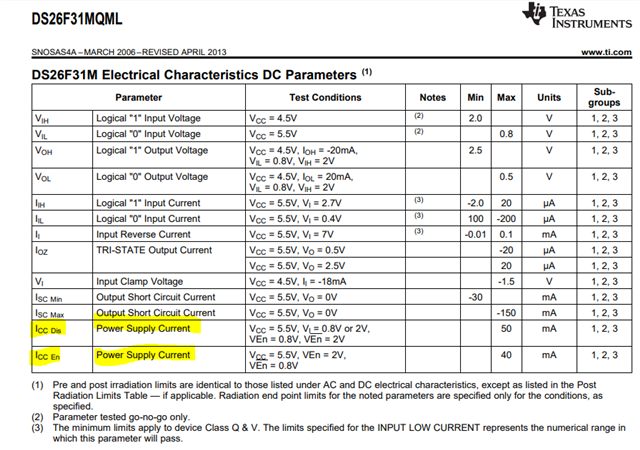

禁用电流高于器件上的使能电流:

这是由于逻辑电路在禁用状态下分流的电流比启用状态多。 这在器件中并不是很常见-但对于该器件、数据表会说明它的工作方式。 最大程度地减小电流是仅在这些使能引脚上放置0V 或 VCC (接近阈值时、电流会针对 ICC 进行分流)、因为该测试使用阈值、这将导致电流更大。

您谈论的是哪个引脚、使 SEU 发生在哪个引脚上? 如果 SEU 甚至发生在其中一个 DI 引脚上并且驱动器被禁用、它将不会在总线上传输-如果您谈论其他事情、请告诉我!

如果您有任何其他问题、请随时联系我们!

最棒的

Parker Dodson

您好、Parker、

感谢你的答复。

"您谈论的是哪个引脚、使 SEU 发生在哪个引脚上? 如果 SEU 甚至发生在其中一个 DI 引脚上并且驱动器被禁用、它将不会在总线上传输-如果您谈论其他事情、请告诉我!"

是的、我们想知道这样的东西。 实际上、由于 此 IC 没有辐射报告、 因此当 SEU 发生时、我们不知道引脚上的故障特性。 如果您可以共享此 IC 的辐射测试报告、那将会非常好。 现在、我们似乎只能讨论 IC 在辐射下出现故障模式的可能性。 例如、如果 DI 或 DO 引脚卡在@1或卡在@0、我们能否通过输出引脚的禁用-使能周期来消除这种情况? 或者、我们是否需要重启电源以消除 DI 和 DO 引脚上的持续故障(卡死@1或卡死@0故障)?

此致、

Zafer Çalışkan è s

您好、Zafer、

产品页面上有辐射报告:

这是我们为此部件提供的辐射报告。

对于 SEU -我不认为该器件对 SEU 如此敏感、因为它没有存储器或寄存器-器件的状态是主动输入的状态。

如果您提到闩锁事件、因为它更适合故障场景 -则需要对其进行下电上电

最棒的

Parker Dodson

您好、Parker、

感谢你的答复。

"对于 SEU -我不认为该器件对 SEU 如此敏感、因为它没有存储器或寄存器-器件的状态是主动输入的状态。"

IC 上没有存储器/寄存器、但发送器内部的逻辑门如何? 它们是否像组合逻辑? 如果是、则只能进行设置、对吧?

"如果您所指的闩锁事件更适合故障场景 -则需要对其进行下电上电"

DS26F31MCML-SP 是否有可能发生闩锁? 因为 IC 的数据表中没有这方面的信息。 如果这确实可行、 我们需要采取一些预防措施、例如将 LCL 电路置于 IC 电源引脚。 那么、您能不能再提供一些有关这方面的信息吗?

此致、

Zafer Çalışkan è s

您好、Zafer、

对于您的第一个问题-是的、您答对了、有一定程度的组合逻辑。 但是没有什么保存状态-根据我的理解、SEU 的原因是更改单个位导致顺序逻辑电路中的状态变化(因此寄存器/存储器具有锁存器和触发器、并且无需不断驱动即可保存状态) 由于状态是主动驱动的、因此没有要更改的保存状态。 话虽如此-我确实认为可以在该引脚上设置一个设置。

因此、一般来说、如果器件未明确声明其抗闩锁效应、则可能不会。 双极和 CMOS 工艺(任何 P 型和 N 型器件都不在井/基板之间有绝缘沟或使用护圈)都可能导致闩锁、因此需要相当一致的设计工作来防止闩锁。 当 满足以下条件之一时、寄生结构(晶闸管)通常会在 VCC 和 GND 之间形成低阻抗路径:

引脚电压上升至高于 VCC 电压、从而开启寄生结构。

2.高于额定值的注入电流进入 GND/VCC 以外的引脚

ESD 事件(不太可能导致闩锁、但可能;这取决于电荷载体在事件后耗散的速度)

VCC 引脚上的大瞬态-最好在瞬态期间将此电压保持在最大额定值以下。

5.应用大于 rec 的 电压电源。

6.电离辐射可能会触发闩锁事件(按照器件上提供的辐射限制使用时不应闩锁)

前五项通常可以在实际设计过程中考虑、因为它基本上可以归结为-不要超过额定值。 如果辐射限制得到遵守、第6项不应成为太大的问题。 我在上次响应中提供的报告显示了关键规格随应用不同辐射水平而发生的变化。

如果您有任何疑问、请告诉我!

最棒的

Parker Dodson

您好、Parker、

我们检查了以下链接后、发现 DS26F31是双极的。 如果该信息正确、由于双极组件不受 SEL 影响、我们处于安全状态。 但是、从您的意见来看、SEL 似乎与器件暴露的 TID 级别相关(如果我的理解是正确的?)。 通常、对于单粒子效应(请参阅)、我们需要检查给定 LET 级别的横截面图。 但请参阅、没有辐射报告。 请您向我们提供相关信息吗?

此致、

Zafer Çalışkan è s

您好、Zafer、

它是双极性的-但它包含 PNP 和 NPN 器件-如果有任何 PNPN 结形式-则可以闩锁;它在 CMOS 中比双极技术更常见-但它不是不可能的。 您链接的线程引用了一篇 IEEE 论文、该论文测试了一个非常相似的器件、但该论文并未指出 SEL 是不可能的-它只是指出在测试的边界内它不会闩锁-但是没有显示横截面、因此无法进行确定 如果有可能形成寄生 PNPN 结-在测试限制下、这不应该是我在上一篇文章中提到的问题。 此外、如果您谷歌搜索"AE Council 双极闩锁"、您应该会找到一篇有关 双极技术如何 导致闩锁的详细文章。 我无法分享我们没有公开的内容(因此基板设计和电路内部)、但在经过测试的条件下、应该可以、SEL 不是问题。

2. SEL 可能有多种根本原因-包括辐射。 在链接的主题上、引用的 IEEE 论文中包含有关 SEL 的数据-此器件使用非常相似的架构、因此在额定条件下、这不是一个问题。

3.最接近的辐射报告是该主题中引用的 IEEE 论文-因为他们测试了一个类似的器件以供参考。 有关此部件的特定报告在产品页面上提供、这是可用的信息。

最棒的

Parker Dodson