Other Parts Discussed in Thread: TL16C750E

大家好、

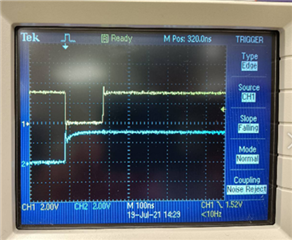

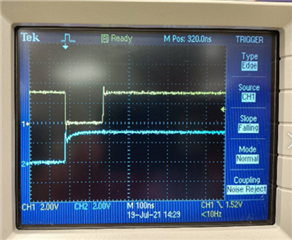

我们尝试使用 MCU 从 TL16C750E 读回寄存器、但发现上升沿缓慢上升、导致 MCU 侧出现错误。 不过、当写入 TL16C750E 时、上升沿看起来正常。 原因可能是什么?

阅读:

写入

谢谢!

罗伊

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Roy、

我认为您可能已经上传了原始帖子中的相同图像、因为两张图片的时间戳都是14:29。 您能否提供另一张图片和标签、说明哪一张被读取、哪一张被写入?

是否还可以在示波器(IOW/IOR)上获取其他信号?

我猜这里的原因是 D0可能会从提供的图像中的输入转换为输出、并且 CS 的快速下降沿和可能靠近 PCB 上 CS 迹线的 D0迹线可能会导致串扰暂时将 D0推至低电平。 由于示波器的分辨率/采样率、我们可能看不到 D0引脚上的完全下降/下降。 对于读取操作、从 MCU 中我不会期望这会导致问题。

-Bobby