主题中讨论的其他器件: DSI 调谐器

尊敬的 TI 专家:

我已经看到了有关如何使用 DSI 调谐器配置 SN65DSI84的常见问题解答。 我已经尝试为 我们的1280x1024p@60fps 显示配置具有单路4通道 DSI /双路 LVDS 的 SN65DSI84、但我还有一些问题。

据我了解、我们的 DSI 时钟频率是固定的、因为连接到 SN65 DSI 输入的 SOM 数据表指定每通道1.5Gbps 的频率。 我不确定在 DSI 调谐器中作为 DSI 通道 A CLK 放置什么值。 我的所有尝试似乎都会导致输出选项卡中的值不兼容。

您能告诉我如何从每通道1.5Gbps 的值计算正确的 DSI CLK 频率?

有关 LVDS 和 DSI 特性的相关文档如下所示。

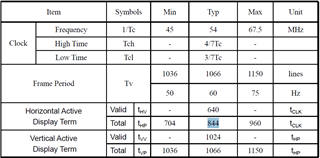

我们的屏幕时间安排:

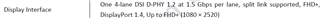

SOM 的 DSI 接口:

提前感谢您的回答、

此致

格伦