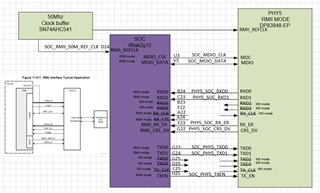

主题中讨论的其他器件: 66AK2G12、 SN74AHC541

您好!

在我的新设计中,PHY DP83848-EP 连接到 FPGA (Xilinx Artix)。

X1 50MHz 参考时钟由 FPGA IO 提供给连接到 X1引脚34的 PHY。

数据表要求时钟在167mS 内保持稳定(表45.7.1 PAG 14)

我假设要求是在上电前和上电后分别切换基准时钟和167mS。

但是,当从 FPGA 获取参考时钟时,由于必须配置 FPGA (87至200ms),因此 FPGA 需要一些时间才能输出时钟,此时 IO 会浮动。

因此、我建议的解决方案是在上电和 FPGA 配置期间保持 PHY 的复位。 只有在 FPGA 开始向 PHY 输出参考时钟后、才会使 PHY 从复位状态中退出。

此方法是否符合上电前具有稳定时钟的请求?

谢谢

Avner