主题中讨论的其他器件:DP83869HM、 DP83869、 TIDA-00928、 TIDA-00496、 TIDA-00306

大家好、

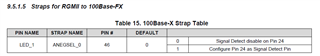

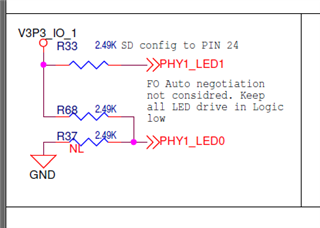

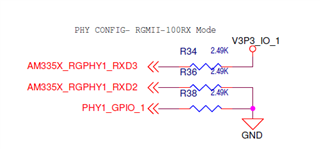

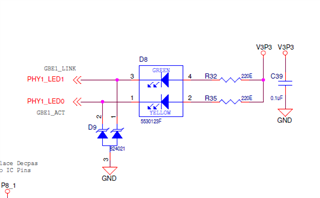

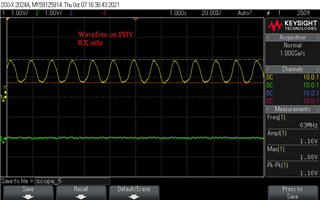

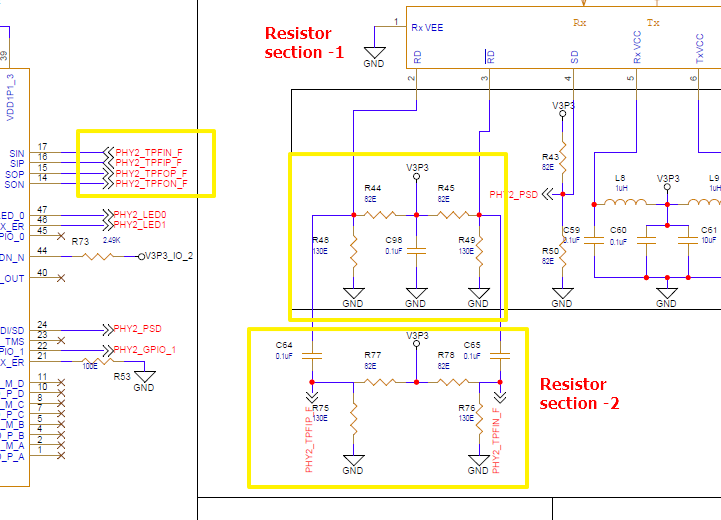

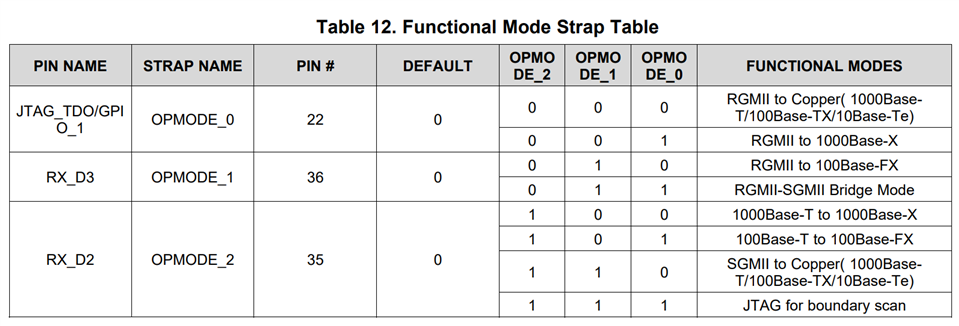

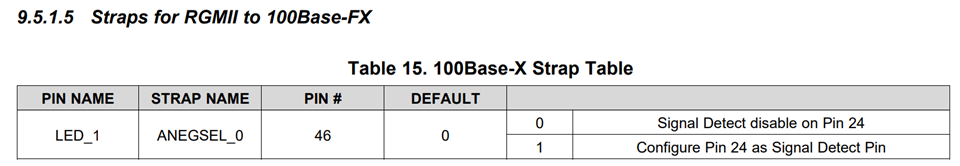

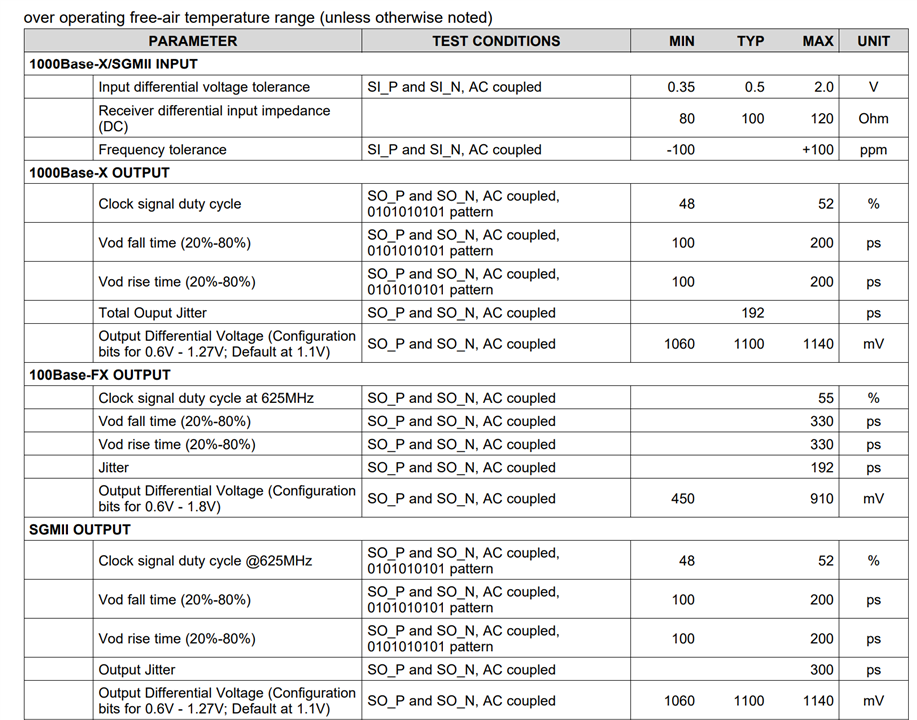

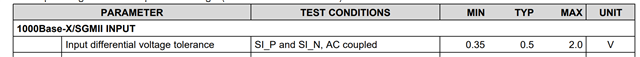

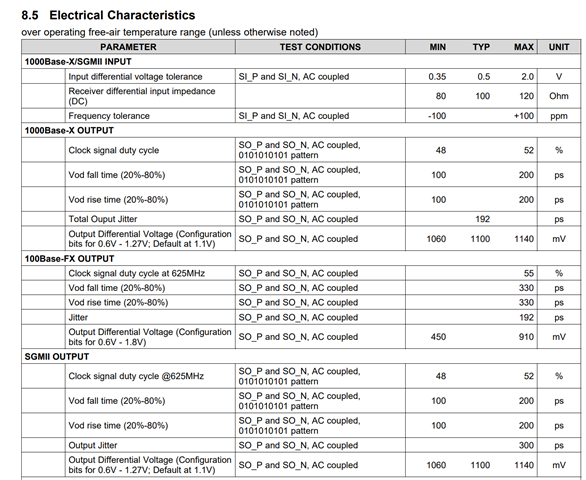

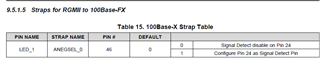

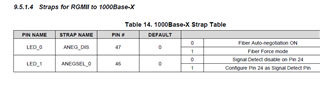

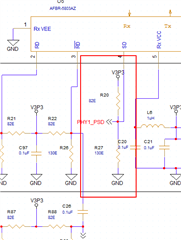

在我的项目中、我需要将 DP83869HM 连接到 AFBR-5803AZ 100FX 光纤模块。

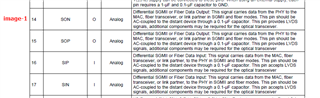

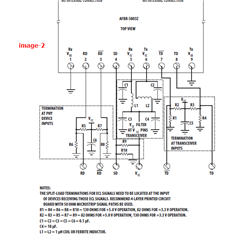

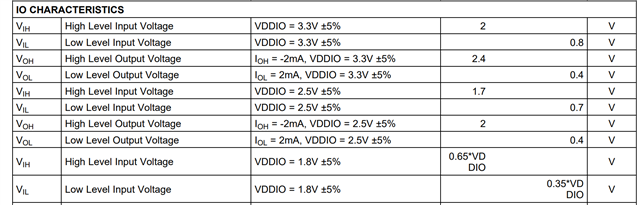

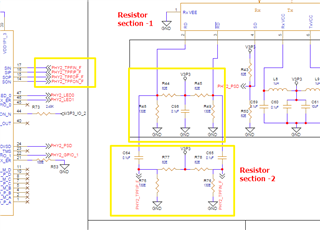

请参阅以下原理图部分、确认 PHY 至光纤信号之间是否需要两组电阻分压器网络。

此外、我还在 PDF format.e2e.ti.com/.../6864.schematic.pdf 中附上了 PHY 和100FX 光纤模块部分的原理图

此致

Anees PK。