请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPD4E001-Q1 您好!

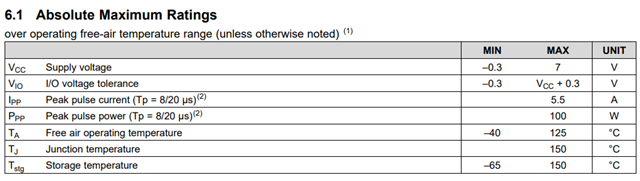

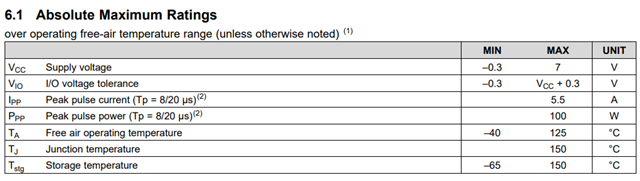

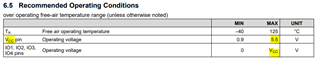

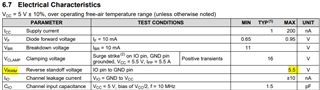

我对该器件的最大"I/O 电压容差"额定值感到困惑。 内部二极管的正向压降似乎约为0.7V (通过我的试验电路板测试)、 而数据表建议在 I/O 引脚上施加的绝对最大电压为 Vcc+0.3V。这不足以使二极管导通。 这是否表明短路电压尖峰是可接受的、而不建议恒定过压超过 Vcc+0.3V?

谢谢、

Sam

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我对该器件的最大"I/O 电压容差"额定值感到困惑。 内部二极管的正向压降似乎约为0.7V (通过我的试验电路板测试)、 而数据表建议在 I/O 引脚上施加的绝对最大电压为 Vcc+0.3V。这不足以使二极管导通。 这是否表明短路电压尖峰是可接受的、而不建议恒定过压超过 Vcc+0.3V?

谢谢、

Sam

尊敬的 Sam:

[引用 userid="539642" URL"~/support/interface-group/interface/f/interface-forum/1158982/tpd4e001-q1-confusing-electrical-ratings-on-datasheet "]是否表明短路电压尖峰是可接受的、而不建议恒定过压超过 Vcc+0.3V?您的理解是正确的。 我们 的 ESD 二极管旨在防止瞬态事件(NS - µs μ s 脉冲持续时间)。它们 不能承受长时间从静态直流电压中分解。 一旦二极管被分解、它会在电流流流过二极管时产生大量热量。 这最终会导致热故障。

因此、我们建议您仅 在额定 Vrwm 或低于 Vrwm 的二极管上施加静态直流电压、在本例中为 5.5V

此致、

Sebastian