你(们)好

我遇到了与 RMII 接收时序异步相关的问题。

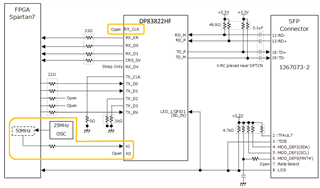

[RMII 设计]

RMII 从器件信号传输。 *MAC = FPGA (Xilinx Spartan7)

=>我连接了 TX_EN、TX_D[1:0]、 RX_D[1:0]、RX_ER、CRS_DV。

RX_DV 和 RX_CLK 未连接。

[故障]

当我用 光纤电缆连接两个已开发的 PCB 板时,MAC->PHY 处的波形是坏的。

=>波形如下

通道1:RXD0

CH2:XI [时钟(50MHz)]

=> RXD0 与时钟异步

*仅 RXD0、波形正确

[问题]

我的 RMII 设计正确吗?

如果正确、 是否存在用于时钟的同步寄存器设置?