请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TFP401A 大家好、

我的客户正在考虑使用 TFP401A。

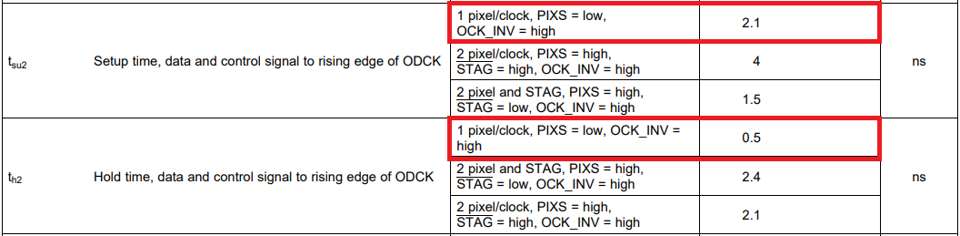

d/s 指定在1像素/时钟、PIX=低电平和 OCT_INV=高电平时的建立时间和保持时间为2.1ns 和0.5ns。 客户注意到这些设置时间和保持时间不能满足 后续级器件的要求、即设置时间4ns 和保持时间1ns。

客户认为 TFP401A 的设置和保持时间很短、因为假定 ODCK 频率高达165MHz。

由于客户使用的 ODCK 频率为50MHz、是否可以放松设置和保持时间?

假定可以放宽的原因是 、当输出 ODCK CLK 高达82.5MHz 时、设置时间为4ns、在以下设置中保持时间为2.4ns。

2像素/时钟像素=高 OCT_INV =高/ stag =低

此致、

山口