主题中讨论的其他器件: TPS74401、 TUSB7340、 TUSB1310

在极少数情况下、当电源打开时、电源线路中会产生连续噪声。

(当电源打开30次时大约一次)

当电源噪声出现时、XHCI 寄存器访问(7.5.3.3.9端口状态和控制寄存器)总是失败。

这种情况的原因可能是什么?

请告诉我可能采取的措施。

如果有有关电源的勘误表、请告知我。

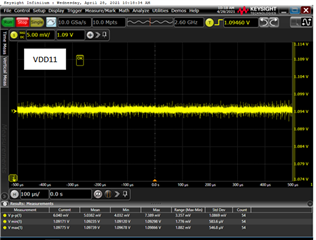

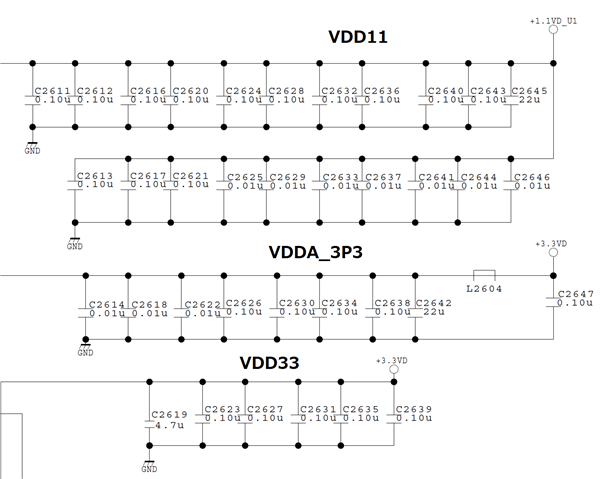

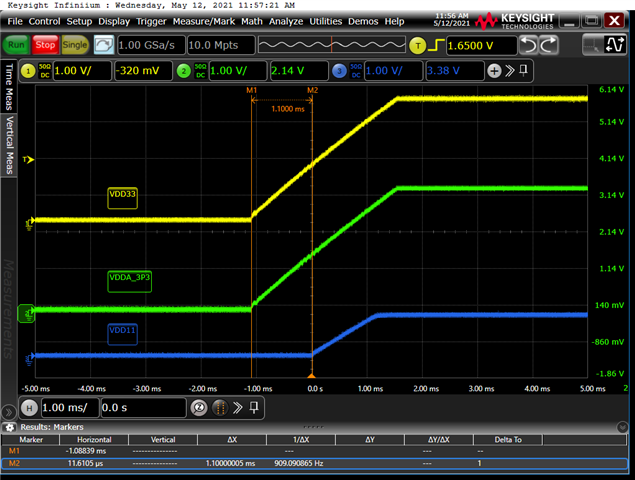

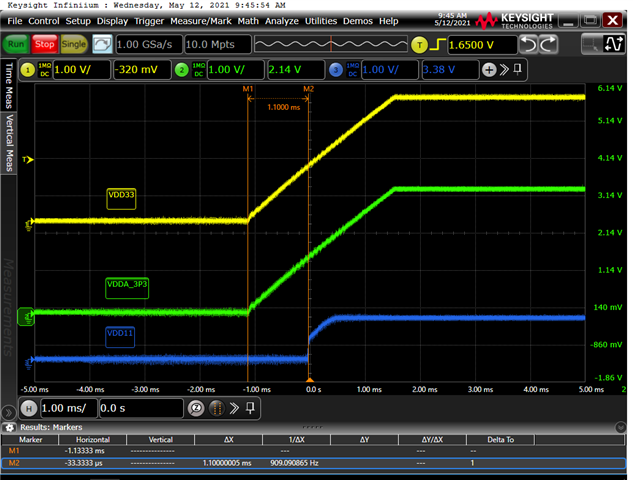

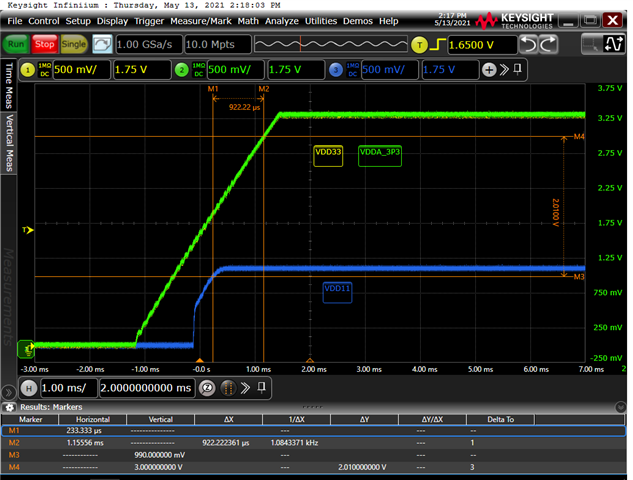

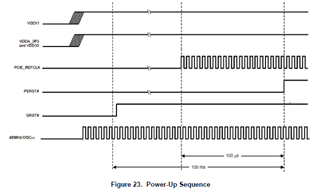

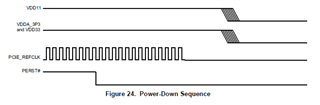

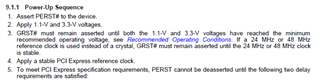

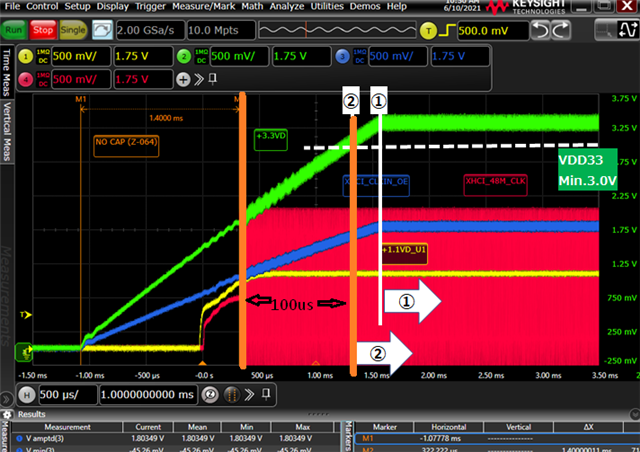

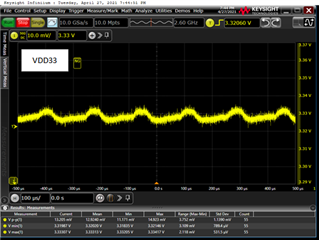

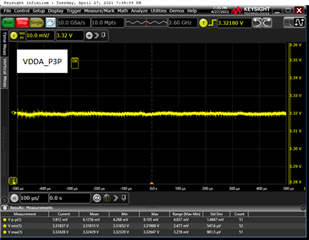

下面是每个正常运行和异常运行的功率波形。

VDD33

正常工作 工作异常

VDDA_3P3

正常工作 工作异常

VDD11

正常工作 工作异常