主题中讨论的其他器件:SN65DSI84

加电并稳定后、我们如何让 DSI CLK 通道处于 HS 状态并让 DSI 数据通道 驱动至 LP11状态?. 我们应该做什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

加电并稳定后、我们如何让 DSI CLK 通道处于 HS 状态并让 DSI 数据通道 驱动至 LP11状态?. 我们应该做什么?

您好 、我是 K:

此致、

陈陆

您好、Chen、

在测试模式下、器件不使用任何输入 DSI 数据。 它仅使用 DSI CLK 或可选的外部 REFCLK。 时钟用于在内部生成图形并将其输出到显示屏

2.在测试图形模式下、无需遵循步骤2和步骤8

3.您可以改为尝试此版本的工具: https://tidrive.ext.ti.com/u/5B25JYQduSH2Hbkl/DSI%20Tuner%202.1.zip?l

此致、

I.K.

您好 、我是 K:

我们有屏幕参数并使用 DSI 调谐器来配置 sn65dsi84。 但现在我们有一些非常紧迫的问题。

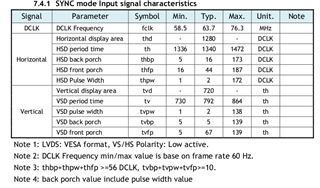

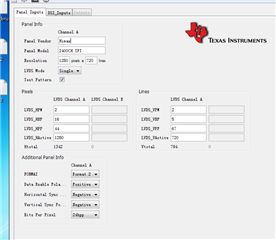

1、我们使用 Flatlink 输出数据(格式2);单链路24 bpp,以下是我们的屏幕参数。

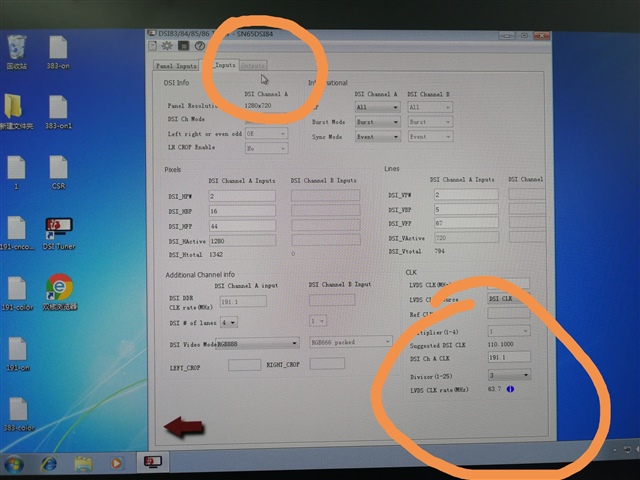

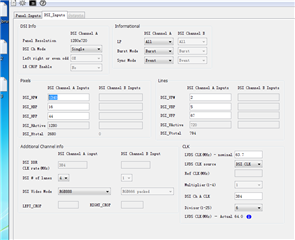

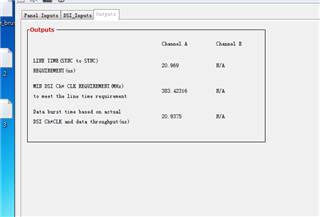

2、以下是我们使用 DSI 调谐器的配置。 为了使 LVDS 线路时间与 DSI 线路时间匹配、我将 DSI_HPW 添加到了1340。 但是、初始化序列完成后、寄存器0xe5等于0x01。 您能告诉我配置是否有问题、如果有、原因是什么?

3、这是我的初始化序列

0D 00 0A

09 00 0A

0A 05 00

0b 28 00

10 26 00

11 00 00

12 4 c 00

13 00 00

18 78 00

19 00 00

1A 03 00

1B 00 00

20 00 00 /* width-l (a)*/

21 05 00 /* width-h (a)*/

22 00 00 /* width-l (b)*/

23 00 00 /* width-h (b)*/

24 d0 00 /*身高-l (a)*/

25 02 00 /* Height-h (a)*/

26 00 00 /*身高-l (b)*/

27 00 00 /*身高-h (b)*/

28 B1 00 /*同步延迟低电平(A)*/

29 02 00 //*同步延迟高电平(A)*/

2A 00 /*同步延迟低电平(b)*/

2B 00 /*同步延迟高电平(b)*/

2C 02 00 /* hpw-l (a)*/

2D 00 /* hpw-h (a)*/

2E 00 /* hpw-l (b)*/

2f 00 /* hpw-h (b)*/

30 02 00 /* vpw-l (a)*/

31 00 00 /* vpw-h (a)*/

32 00 00 /* vpw-l (b)*/

33 00 00 /* vpw-h (b)*/

34 10 00 /* HBP (A)*/

35 00 00 /* HBP (b)*/

36 05 00 /* VBP (A)*/

37 00 00 /* VBP (b)*/

38 2c 00 /* HFP (a)*/

39 00 00 /* HFP (b)*/

3A 43 00 /* VFP (A)*/

3B 00 /* VFP (b)*/

3c 10 00 /* bit4通道 A 测试模式;bit0 -通道 b 测试模式*/

3D 00

3e 00 00

0D 01 0A

09 01 0A

FF 00

E5 ff 0a];

此致、

陈陆

您好、Lu、

您的设置不正确- DSI CLK 应为191.1 MHz。 此外、LVDS 端的像素/线条设置必须与 DSI 端的像素/线条设置相匹配。 请参考此培训视频以正确配置器件: https://training.ti.com/configuring-sn65dsi8x-single-channel-dsi-single-link-lvds-operation

此致、

I.K.