大家好、

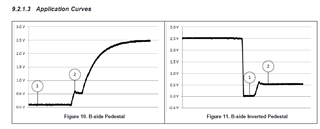

在数据表9617A 中、下面显示的两个图(图10和11)是 B 侧出现的基座曲线。 有人会解释一下、在哪两种情况下、这些命运会发生、因为它们并不相同? 它们是针对不同的 I2C 操作模式、还是在相同的操作模式下使用不同的上拉电阻器绘制的曲线? 在这两种情况下、数据表都没有提到设置环境。 请解释它们有何不同?

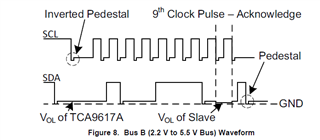

另一个问题是、图8中的基座和反相基座分别与 SDA 和 SCL 线一起显示。 支架是否仅与 SDA 关联、与 SCL 关联的反向支架?

感谢你的帮助。

uF

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

在数据表9617A 中、下面显示的两个图(图10和11)是 B 侧出现的基座曲线。 有人会解释一下、在哪两种情况下、这些命运会发生、因为它们并不相同? 它们是针对不同的 I2C 操作模式、还是在相同的操作模式下使用不同的上拉电阻器绘制的曲线? 在这两种情况下、数据表都没有提到设置环境。 请解释它们有何不同?

另一个问题是、图8中的基座和反相基座分别与 SDA 和 SCL 线一起显示。 支架是否仅与 SDA 关联、与 SCL 关联的反向支架?

感谢你的帮助。

uF

"有人会解释一下、在哪两种情况下、这些命运会发生、因为它们并不相同? "

图10是 B 侧驱动为低电平但随后释放时的上升沿(例如、如果 I2C 器件/响应器位于 B 侧且正在进行应答或在读取事务期间向主机发送数据)、 此基座由内部逻辑生成、该逻辑要求一端高于阈值、然后才能完全释放并上升到 B 侧。 因此、如果您从 B 侧驱动、则需要等待 A 侧超过电压阈值、此时 B 侧希望释放电压、然后才能完全上升。

图11显示了下降时间加速器(当 A 侧驱动为低电平、而 B 侧为高电平时)、这是释放到失调电压之前暂时下拉至 GND (这将一直持续到 A 侧释放)。 这是在容性负载较重的情况下实现的、同时也可以加快传播延迟。

" 它们是针对不同的 I2C 操作模式进行的、还是在相同的操作模式下但使用不同的上拉电阻器进行的曲线?"

不、它们只是从不同的角度看待。 图10是 B 侧驱动低电平并释放的情况。 图11是一侧驱动低电平的情况。

"在这两种情况下、数据表都没有提到设置环境。 请解释它们有何不同? "

唯一的设置差异是哪一侧正在行驶。 上拉和工作速度不会改变这种情况。

"另一个问题是、图8中的基座和反相基座分别专门用 SDA 和 SCL 线显示。 基座是否仅与 SDA 关联、与 SCL 关联的反向基座?"

我喜欢这个问题、它不会经常被问及。 SCL 通常是单向的、因此、如果您的 A 侧是 I2C 主机、B 侧是 I2C 器件/响应器、那么您 看到的唯一基座类型将是图11中的基座类型。 如果我们交换主机和响应器、主机位于 B 侧、响应器/器件位于 A 侧、则可以看到图10的基座。

SDA 在事务中的某个点将具有两个阻抗、但根据主机位于哪一侧(B 或 A)、相对于 I2C 器件/响应器、您将看到一个比另一个阻抗多。

-Bobby