Other Parts Discussed in Thread: DPHY440SSRHREVM

主题中讨论的其他器件:DPHY440SSRHREVM

您好!

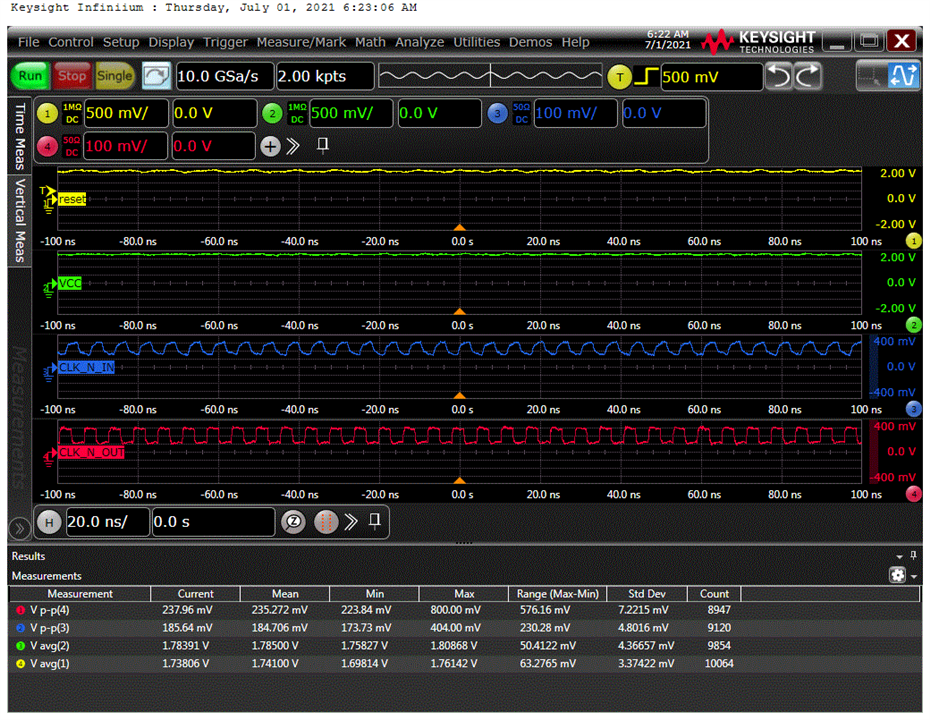

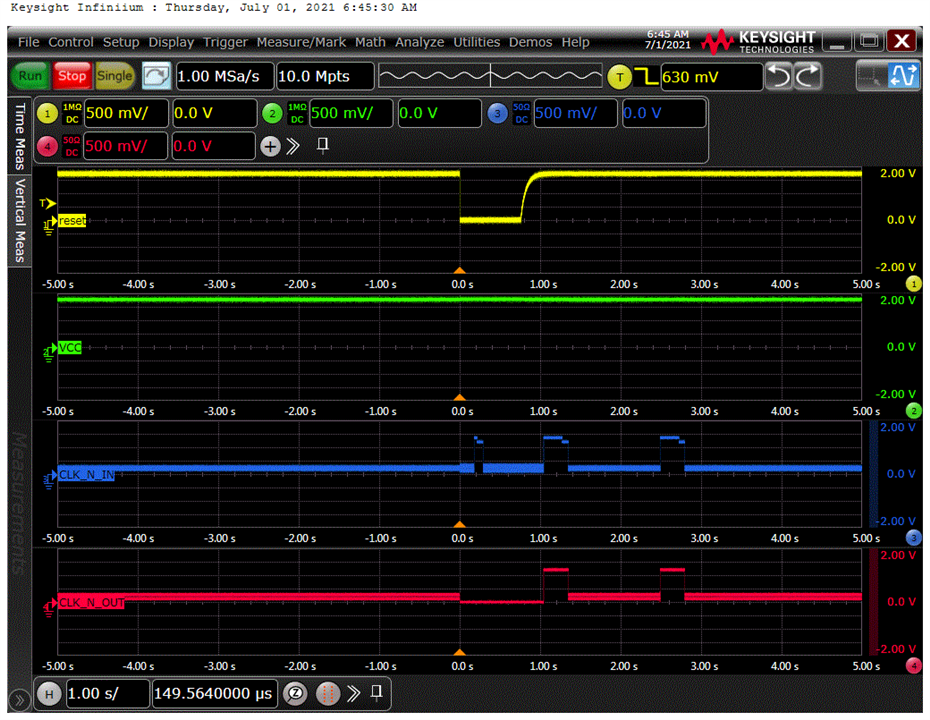

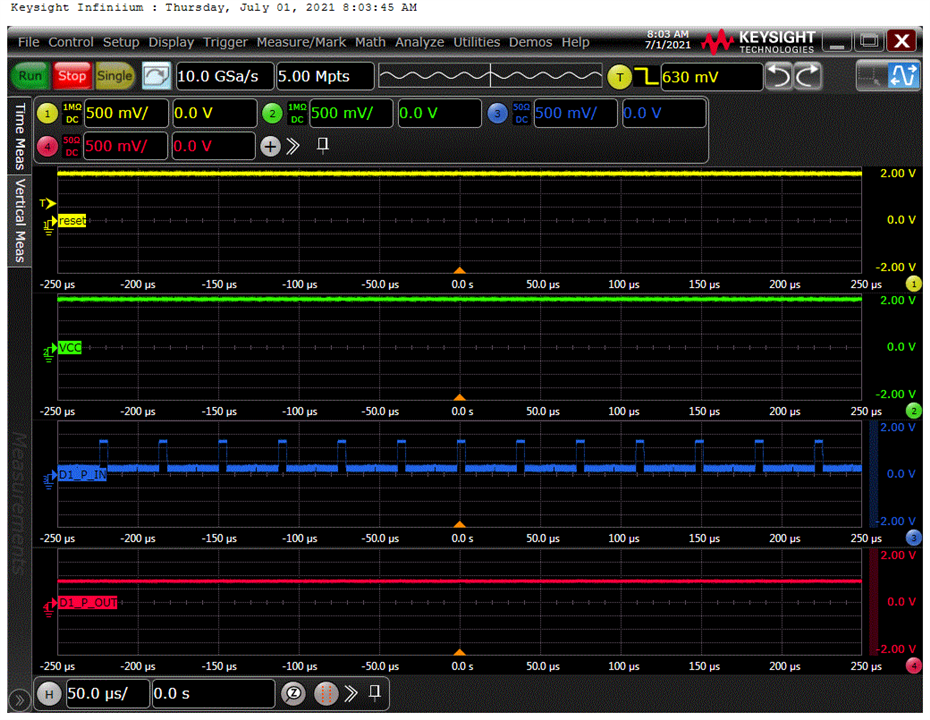

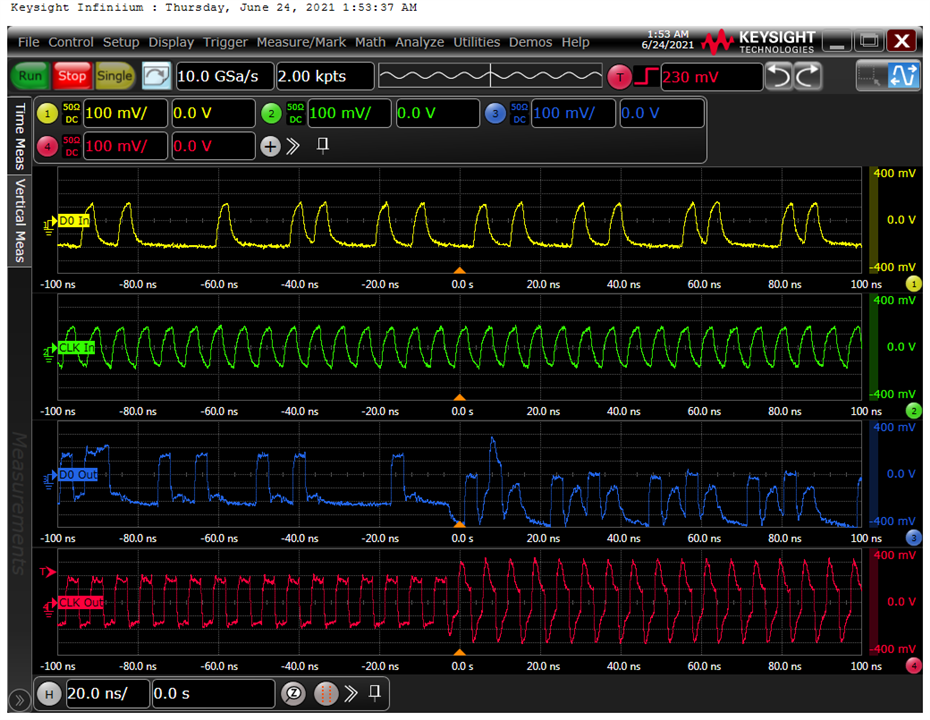

我遇到了这个部件的问题。 首先是一个小故事。 我已经使用评估板验证了该部件在我的系统中是否正常工作。 现在、我已将重定时器 IC 放入具有相同配置的 PCB 中、但它不再工作。 我已验证数据和时钟正在通过重定时器、并且似乎按预期输出。 但是、我注意到的一个有趣的现象是、输出驱动器似乎意外(定期)改变了其驱动条件。 请参阅随附的示波器捕获。  您可以看到、输入数据和时钟信号并未改变、但输出会经历驱动变化。

您可以看到、输入数据和时钟信号并未改变、但输出会经历驱动变化。

感谢您的任何帮助。

谢谢、

Nathan