您好!

我正在运行裸机 C 应用的定制 PCB 上以 RMII 模式连接 DP83822IF。

我将 PCB 与 phy 配合使用了一段时间、并认为我成功地对其进行了正确设置、但在过去的几天中、我观察到了意外行为。 通常、以太网通信按预期工作、但正如我在 TCP 接口上执行了一些严重的应力测试一样、我注意到在重新传输过程中遇到某种故障时、TCP 堆栈会挂起。

在我的故障排除中、我还观察到 PHY 监视其寄存器的行为、并发现一些可疑信息:

- 错误载波事件计数器(寄存器 FCSCR 0x0014)正在持续递增

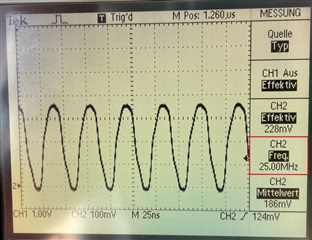

- 接收错误计数器(寄存器 RECR 0x0015)也在持续递增(我通过 PHY 的 RX_ER 引脚验证了计数器、并观察到该信号上确实有持续脉冲)

- 当在 phy 上启用可用中断时、我还会观察到频繁但非周期性的链路质量中断

正如我说过的、界面一般似乎正常工作、即使在 phy 上观察到"错误"、但我不确定 phy 上述行为的严重性。

除了上述观察结果之外、我还测试了另外一件事:

启用快速下行链路事件时、我会观察到从上行链路到下行链路的持续变化、反之亦然。 附加的能量检测中断会跟随每个链路断开事件以及几个 MDI 交叉更改中断(~6-12次)、有时极性更改中断也会附加到列表中。

产生的链路上下拉必然会阻止以太网连接的正常使用、但我仍然认为在这种模式下、链路问题不应像我所观察到的那样多。

您能告诉我观察到的 PHY 行为是否看起来是绝对的"正常现象"、还是指出了一些配置错误(在硬件或软件配置中)?

什么可能导致此类行为?

提前感谢您!

此致、

Julian