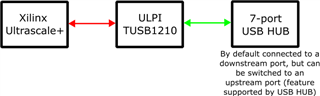

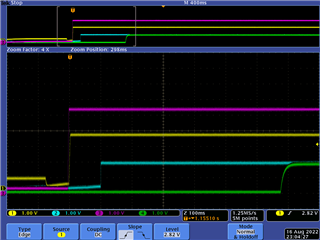

在 过去的几周中、由于 USB 问题、我忙于调试新的 PCBA。 我们使用的是 Xilinx Ultrascale+ FPGA、USB 2.0器件连接到 TI TUSB1210。 但出于某种原因、我们无法检测到一个板(约90%)、位于该 ULPI 器件之后的 USB 集线器(在 uboot 中获得"无法复位端口1")。 在调试集线器设置和焊点(X 射线检查)后、此部件上未发现问题。 我已经检查了 ULPI 接口并检查了信号质量、这里我注意到一些中间化电平(0.9V 而非0V 或1.8V、请参阅随附的示波器图)。

蓝色=数据[4]、在 ULPI 引脚7上测量、黄色= DIR、在 ULPI 引脚31上测量、紫色=数据[4]、在引脚7上测量、但使用有源探头进行测量、用于检查信号完整性。 但没关系

TI 能否告诉我们这是 ULPI 接口的正常行为(在 ULPI 规范中找不到什么)、还是我们在总线上遇到某种冲突? 如果 这种错误行为、那么我可能会发现我们的大多数板无法正常工作、有些板无法正常工作。

此致、Pieter