Other Parts Discussed in Thread: DS50PCI402

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/944595/ds50pci402-ds50pci402

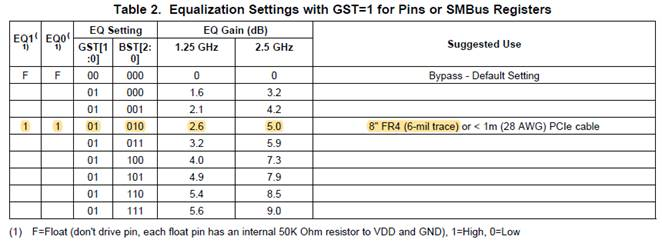

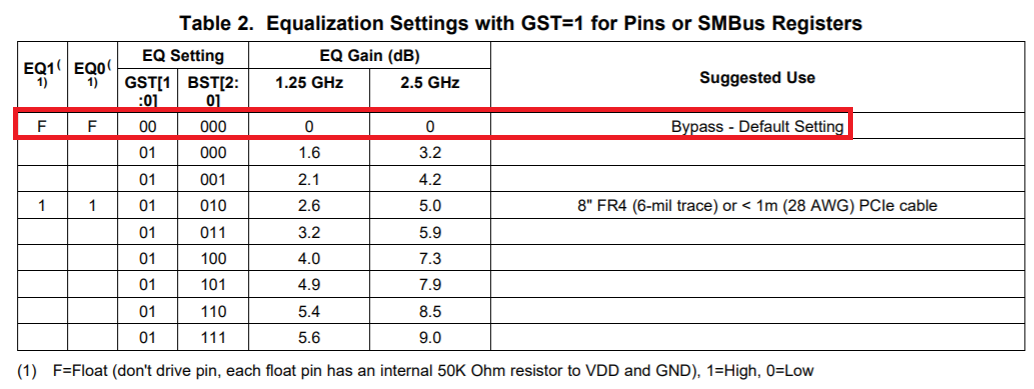

器件型号:DS50PCI402尊敬的技术支持团队:

我一直在尝试以下问题。

我尝试了各种设置、但没有解决链接问题的组合。 即使在旁路模式下也是 NG。

因此、当 DS50PCI402被移除并与接插线连接时、连接问题得到了改善。

如果接线长度较短、是否可能会出现问题?

目前、布线长度在10 cm 以内。

此致、

TTD