https://e2e.ti.com/support/interface-group/interface/f/interface-forum/760576/sn75176b-sn75176b

器件型号:SN75176B主题中讨论的其他器件: THVD1550

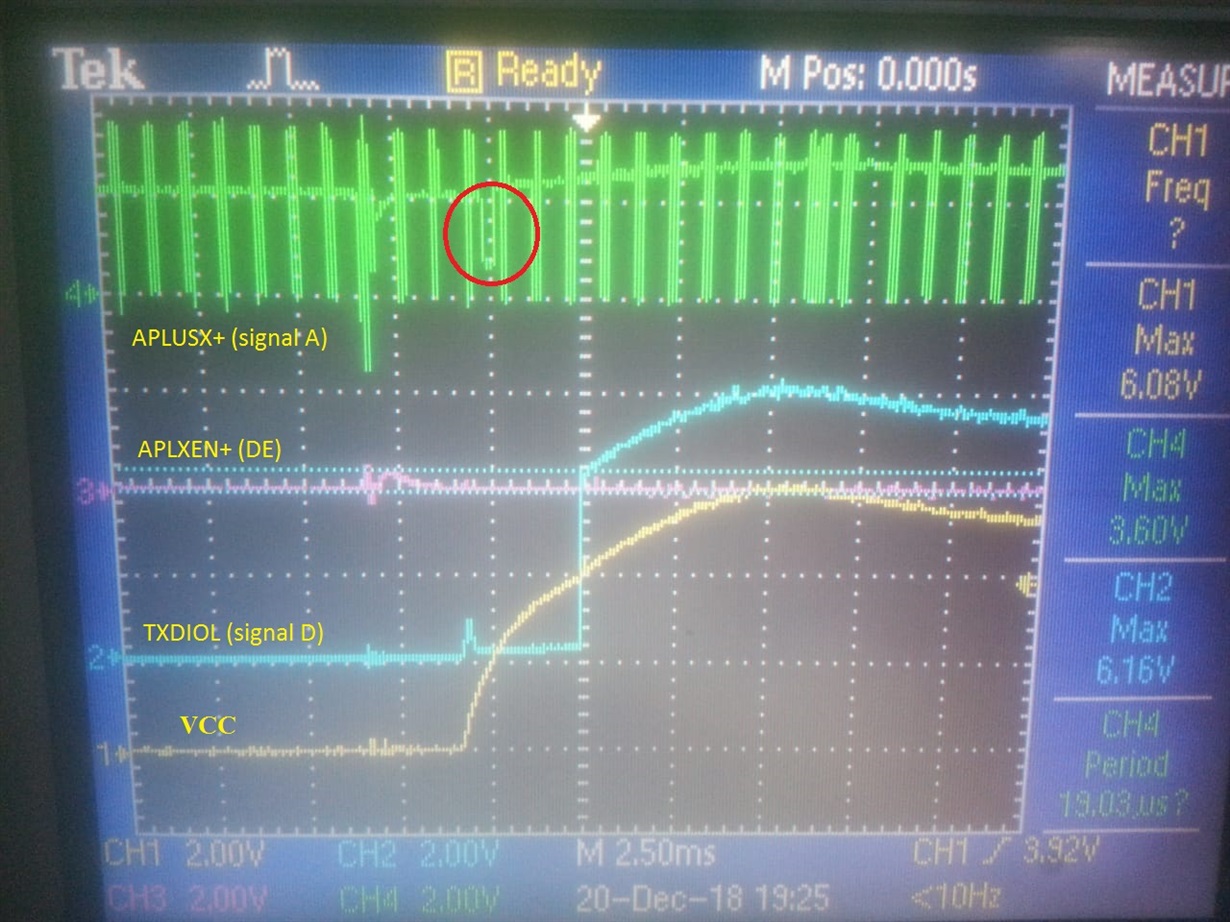

我在一个具有 UC AT89S52-24U 的输入模块中使用 SN75176B 差动总线收发器。 我在差分 RS-485通信中遇到错误。 我已连接捕获的 SN75176B 信号。 我在‘信号(RS 485,信号“A”,通道4)中观察到干扰,当 DE (通道3)为低电平时,在信号 D (通道2)变为高电平之前,由于这种情况,我们会遇到通信错误。 这种情况在每次加电状态时发生、因此、无论模块何时插入系统、我们都会在通信中遇到错误。

实际上,当 DE 为低电平时,直至该期间,不应对差分信号‘A’和‘B’产生任何影响。

当我使用 AT89S52-24JU UC 时会发生这种情况、但 NXP UC P80C32 UC 不会出现这种情况。 我已附加这两个方案。 您能否分析 此情况并告知我们发生此情况的原因?