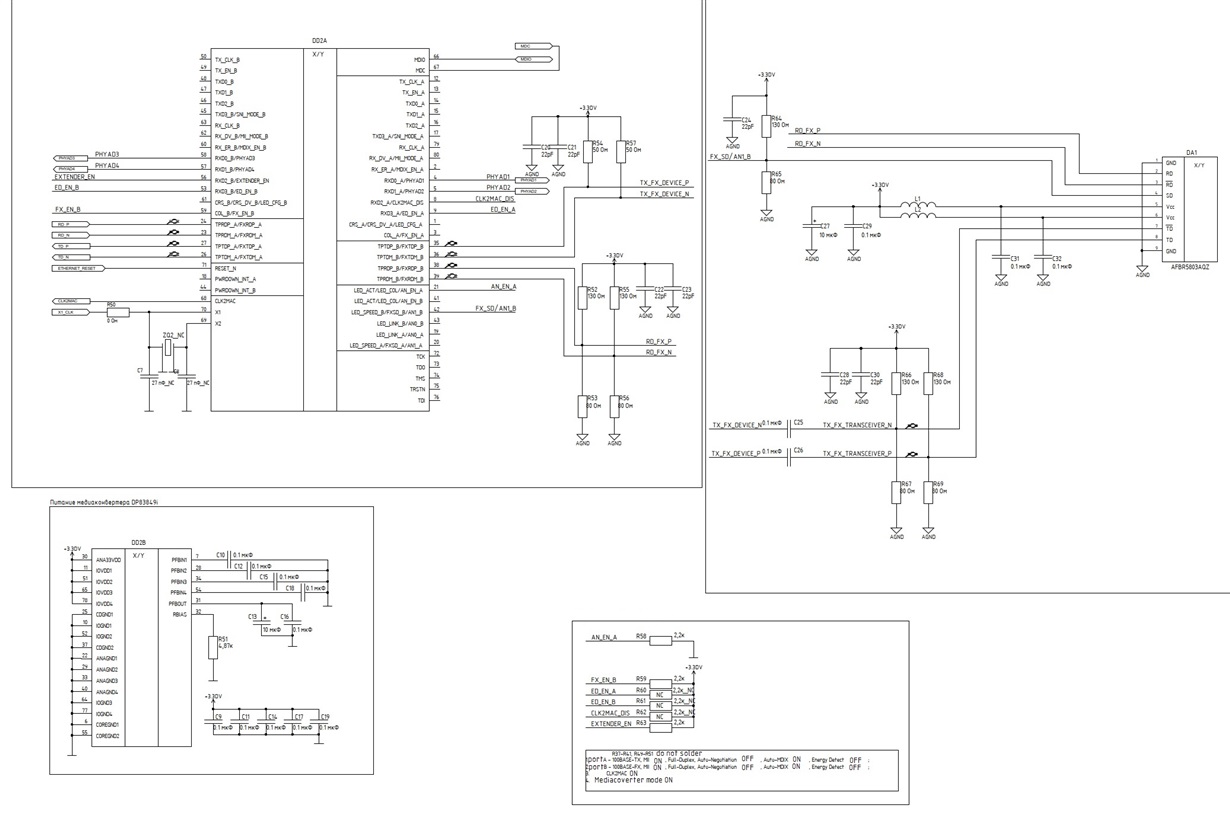

我正在构建光学以太网交换机。 我尝试在介质转换器模式下使用 DP8384IF。 我的板上有多个端口(多个 DP8384IF IC)。 我还有另一个板、上面有光学瞬变器、链路状态和活动 LED (工作正常)。 我已经通过光缆将这些板连接在一起。 问题是、上电时、只建立一半的板链路(有时 可以正常工作、但有时无法正常工作)。 我根据 另一个板上的链路状态和活动 LED 做出这样的结论、同时当状态/活动 LED 关闭时、TX/Rx 差分对上不发送任何数据(甚至不是空闲的 parttern)。 所有 DP8384IF 端口上的行为都类似、其中一些端口的启动频率更低(10个端口中的~ 1个时间)。 我的板上还有其他端口、带有 DP83620SQ/NOPB PHY、它始终工作。 我已附上我的原理图。 我的自举选项位于原理图上。 我已经检查的内容:

1、时钟正常- 25 MHz、预处理清晰。 (虽然我认为 PHY 操作不需要时钟、但会导致时钟恢复、顺便说一下、我对吗?)

电源是3.266V、看起来很清楚。

3、复位为3.3V、低电平有效。 (切换复位不起作用、只有下电上电功能才起作用、因此我认为它不是自举选项)。

此外、我还感到困惑的是、JTAG 引脚、pwrdown_int 引脚等上没有电压(它们在我的方案上浮动、并且根据数据表、它们应该有内部上拉电阻)。

发生什么事了? 端口 B PHY 似乎由于某种原因未启动、但我认为如果有电源、断电高电平、复位高电平(我是对的吗?)、它应该是任何规避方案。 虽然能量检测模式是? 问题出在哪呢? 我的化学文件已附加... 谢谢!)