主题中讨论的其他器件: DS90C032

您好、支持人员、

我们有一个 LVDS 接收器故障(这不是第一个故障)。

研究仍在进行中、但接收器从其 Vcc 引脚汲取的电流为170mA。 在中发生故障的测试过程中驱动的连接对不再起作用、而另一个信号部分工作。 通过并联降低 IC 内的阻抗(几欧姆)、可大大降低失效防护电阻。

我们认为这是因为发送器和接收器模块之间缺乏可靠的接地参考。

-接收器壳体模块回路电源已连接至电源接地

kΩ 器外壳模块接地连接到底盘;底盘平放在 ESD 垫上;MAT 提供一个到测试台的电阻连接、然后直接接地(CPPRX 到接地、使用 DMM 测量为~1 μ m)。

虽然 ESD 垫应该耗散所有静态电荷、但一个瞬态放电事件仍然有可能导致一个差分接地电压。

这些芯片是否经常被视为容易损坏?

TI 如何建议我们最好地保护设计中的芯片?

发送器是否也可能损坏?

我还注意到、数据表中可能存在与此标准相关的不一致之处:

LVDS 接收器"绝对最大额定值"允许最大输入电压(RI+、RI-)为"-0.3V 至+5.8V"(参考:DS90C032QML 数据表、SNLS203D、2013)

自相矛盾的额定值:非 QML 规范中的相同值意味着接收器不得未通电:"-0.3V 至(Vcc +0.3V)"-参考:DS90C032数据表、SNLS094D、2013

假设两种产品使用相同的裸片、上述其中之一是否不正确?

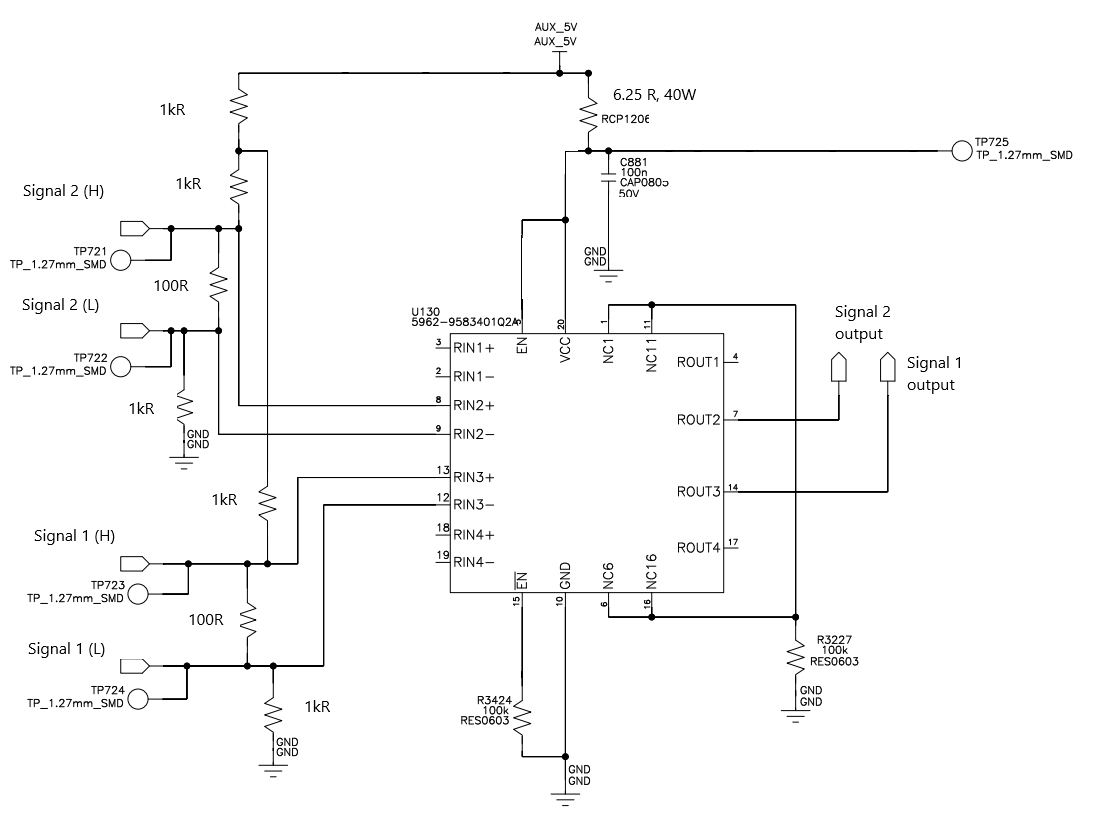

如有需要、请参阅随附的接收器电路简化版原理图。

谢谢。