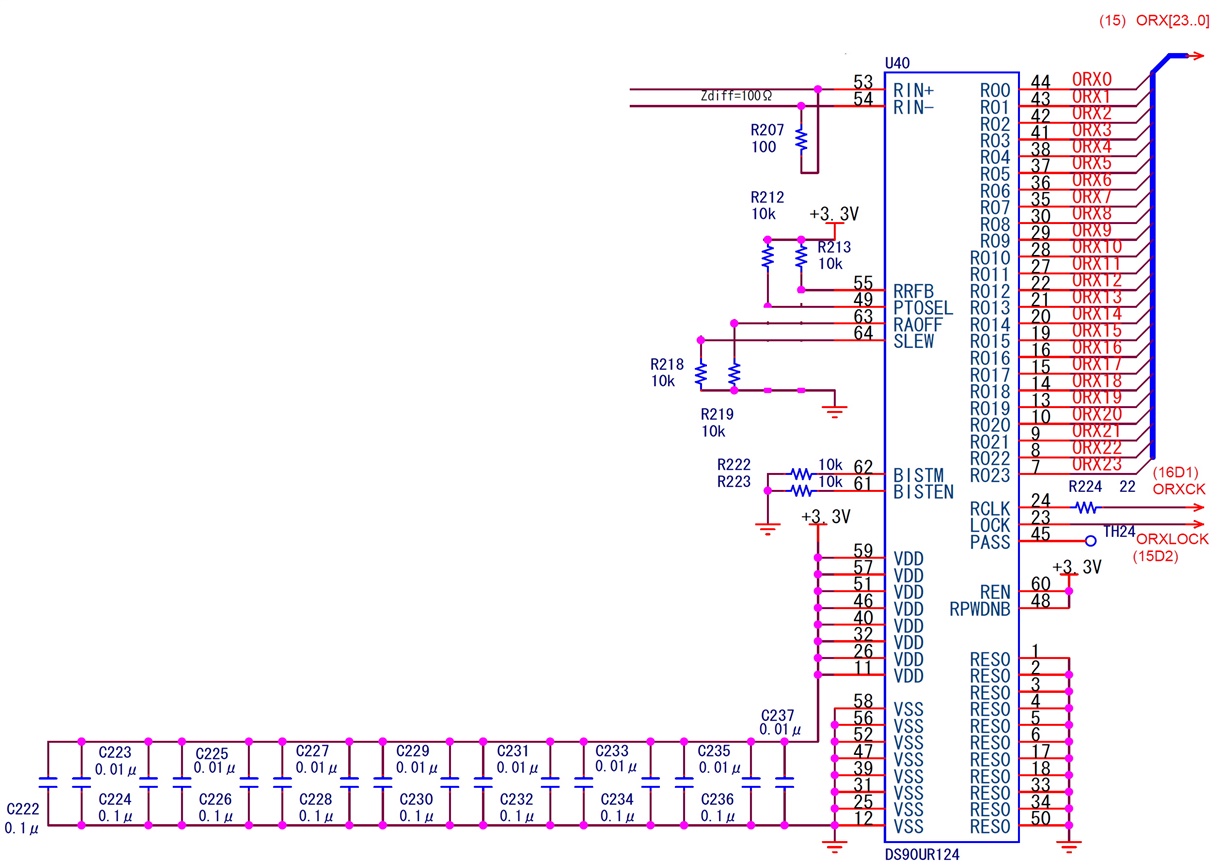

Other Parts Discussed in Thread: DS90UR124

DS90UR124用于通信、但在某些情况下没有输入信号。

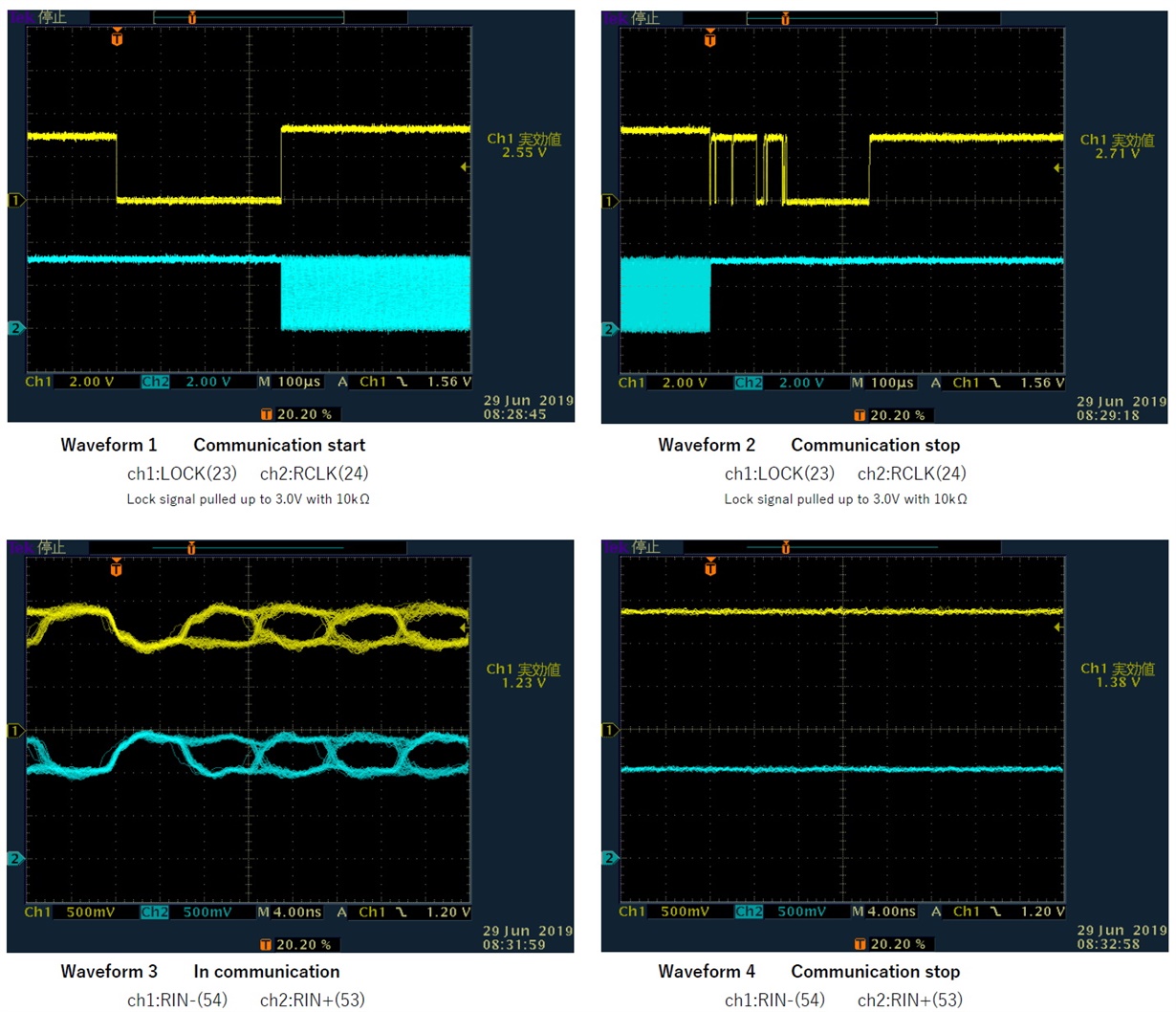

当 RIN+和 RIN-的输入中没有信号时、我认为 LOCK 信号的输出是 L 电平、但它似乎是 Hi-Z

"此外、解串器锁定输出将保持低电平、直到其 PLL 锁定到 Rin±引脚上的传入数据和同步模式。" 数据表第19页。

信号设置固定为 RPWDNB=H、REN=H、RAOFF=L

数据表第23页的表2显示了 PLL 锁定时的锁定= H、而未锁定时的锁定= L。

我认为锁定信号输出是 L 电平、即使 RIN+和 RIN-输入上没有信号、就像 PLL 未锁定一样、但锁定输出是 Hi-Z

当不处于断电模式时、当 RIN+和 RIN-输入中没有信号时、LOCK 输出是否正确为高阻态?