您好、Sirs、

很抱歉打扰你。

您能帮您仔细检查我们的原理图、如下所示? 欢迎提出任何建议。

原理图:

也需要确认一些问题。

1) 1)我设置为使用自举引脚调整设置。 SCL_CTL / SDA_CTL I2C I/F 是否可以悬空? (无上拉)

2)但我也保留将上述 I2C 连接到 PCH I2C 的可能性、以便 BIOS 设置此 HDMI IC。 此时、这些自举引脚可由自举引脚或 I2C 进行双选。

例如、如何连接 SLEW_CTL 上拉/下拉

EQ_SEL、HDMI_SEL 也设置 I2C 地址、将设置顶部上拉/下拉

其他 I2C_EN、TX_TERM_CTL 具有其他功能或具有上拉/下拉功能

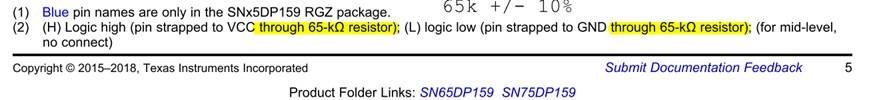

3)自举引脚应使用65K 欧姆电阻器、但该电阻器值不在我们的内部器件库中。 那么、电阻值的允许范围是多少?