请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DS110DF410 您好!

下面我的问题是有关重定时器 DS11DF410的问题、可以帮助您检查并提出一些建议吗? 非常感谢。

- 重定时器芯片具有25M REFCLK 输出。 时钟是如何在芯片内部生成的? 是否从 CDR 恢复? 它是否可以用作 SyncE 的恢复时钟。

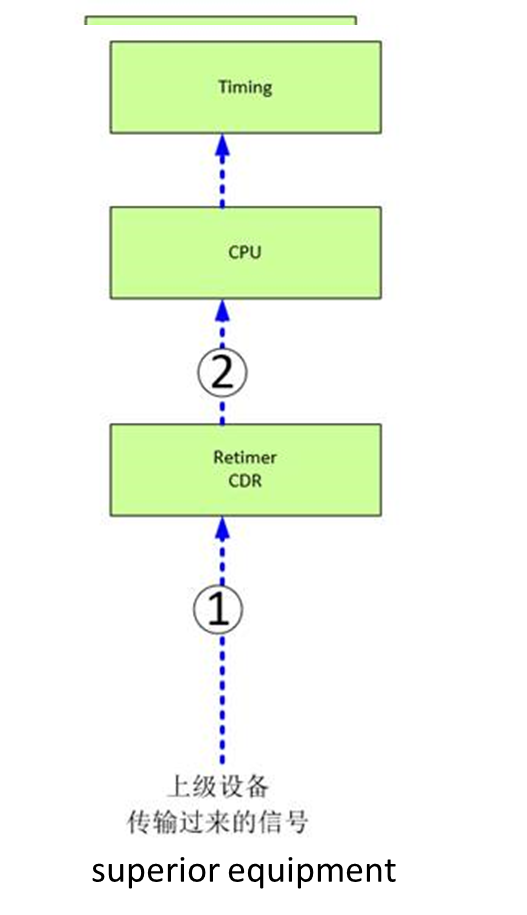

- 如下图所示、向重定时器、内部重定时器发送信号的高级设备将具有 CDR、并恢复时钟、 然后将其发送给 CPU,您能告诉我位置1 (重定时器之前)的时钟与位置2 ( 重定时器之后)的时钟之间的差异吗? (时钟和 PTP 信息是否会因延迟、频率偏差等原因与上层设备不一致?)。 CPU 从 位置2恢复的 SyncE 时钟是否有任何问题? CPU 是否需要通过 I2C 访问重定时器中的 CDR? CPU 在 CDR 中读取一些调整参数来调整重定时器的时钟、以实现与位置1中的时钟的同步?