请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMDS181 尊敬的支持团队:

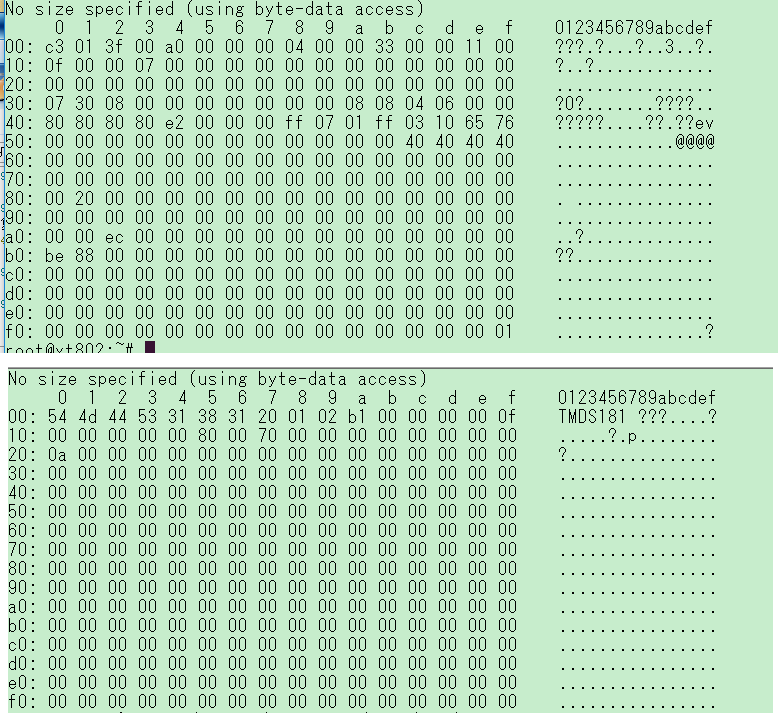

客户使用 TMDS181进行 HDMI 输入、视频源为4kP30 HDMI 信号、数据速率为3.94G、时钟速率为297M。 他们发现、当电缆长度小于1.5米时、情况良好。 而当它为2.8m 时、遵循 TMDS181的 FPGA IP 内核将无法识别视频源。 如果将 TMDS181模式更改为转接驱动模式、则比重定时器模式更好。

它们还使用相同的电缆延长来测试没有181的 FPGA EVK、所用的 EQ 来自 FPGA。 结果非常稳定。

那么、可能的问题是什么? (181的附加抖动是否会导致问题?) 非常感谢!