主题中讨论的其他部件:AM4377、 DP83640

您好!

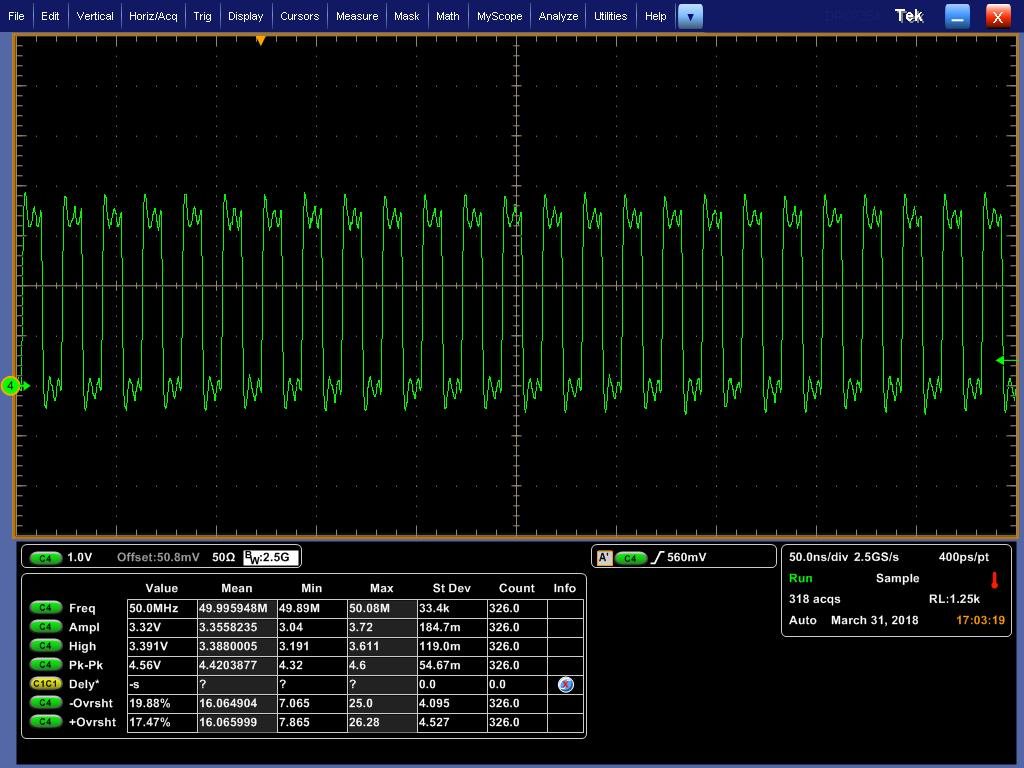

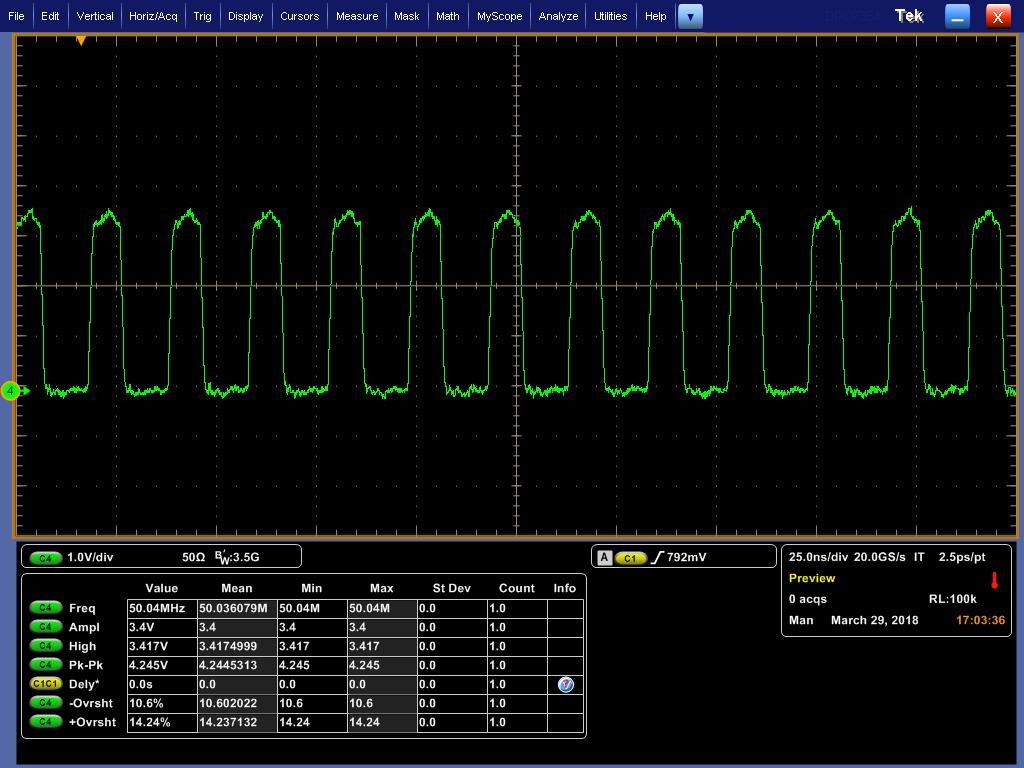

我们正在其中一个项目中使用 TI 的 AM4377 CPU 和 DP83620以太网 PHY。 我们能够提高10Mbps、但在100Mbps 时、数据包丢失率约为30-60%。 我们的测试设置如下所示。

AM4377 CPU 位于主 PCB 中、DP83620以太网 PHY 位于通信 PCB 中。 CPU/MAC 至 PHY 的连接通过 Samtec 卡边缘连接器(PN:HSEC8-120-01-SM-DV-A)进行。 随附以太网 PHY 电路板原理图。 布线长度符合 DP83620 PHY 准则("AN-1469 PHYTER 设计和布局指南"中的< 6英寸)。 随附的布线长度详细信息。

此外、请查找更多问题:

- 请告知我们 TXe2e.ti.com/.../6558.ETHERNET_5F00_LENGTH_5F00_MATCH_5F00_ANALYSIS_5F00_TI.xlsxD_3

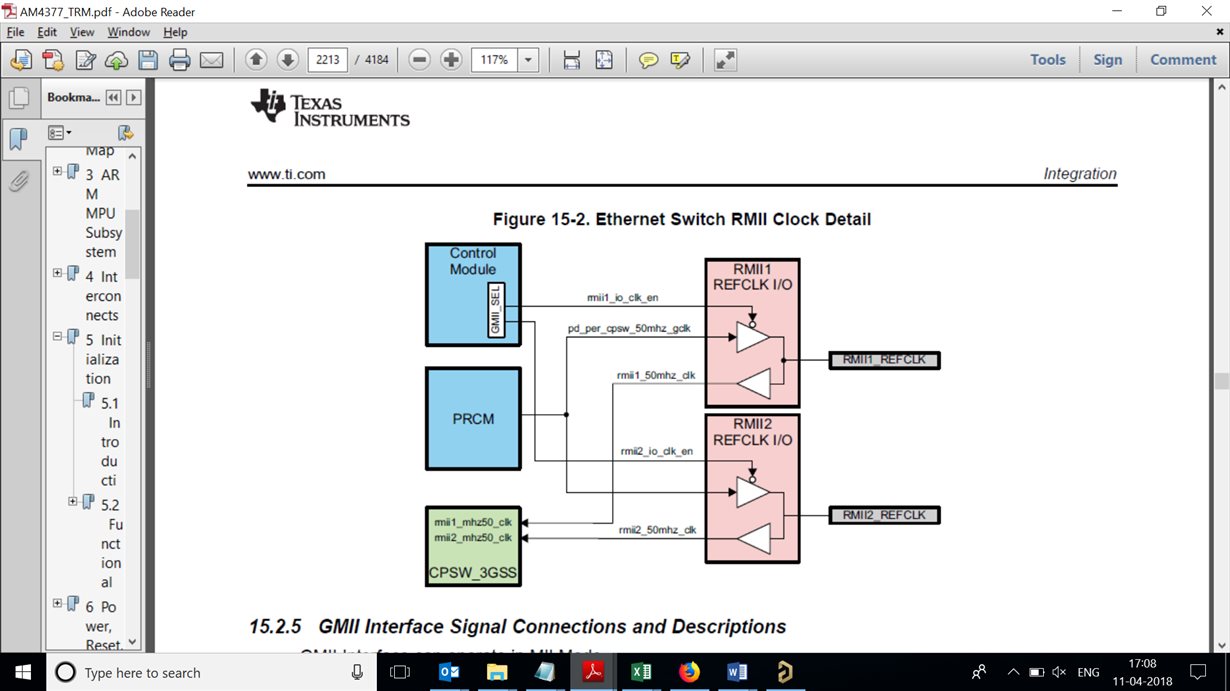

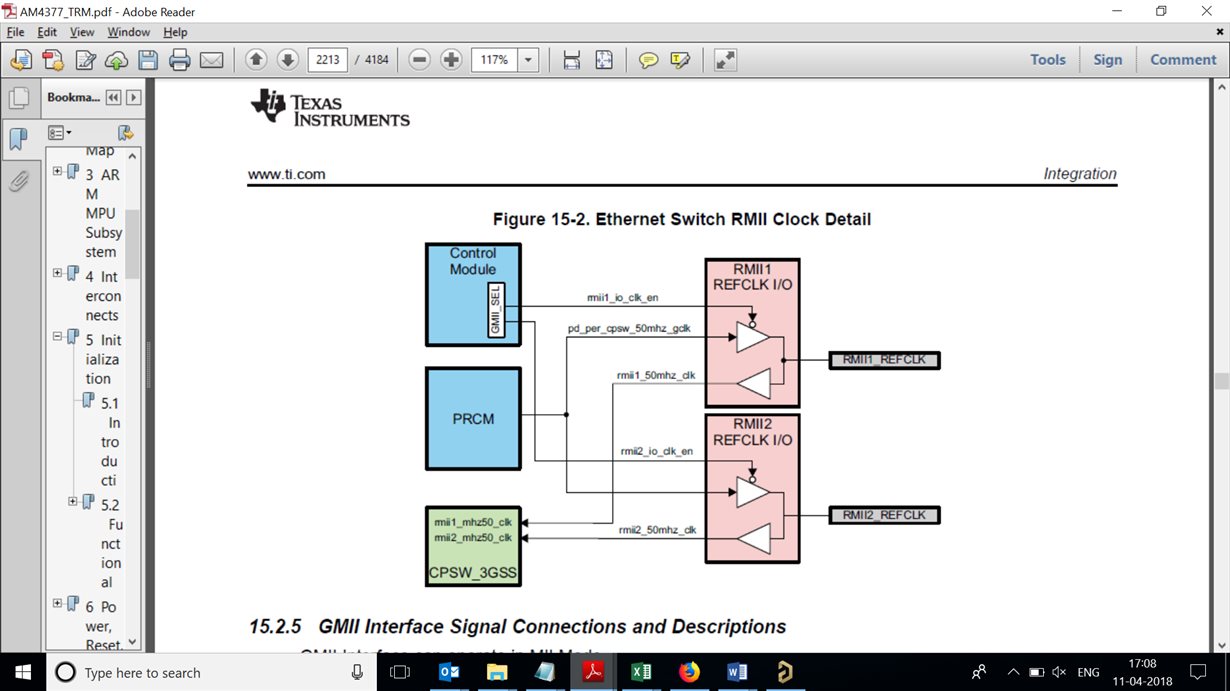

引脚的自举选项(以启用 RMII 从模式)、因为数据表中未明确说明此选项。

引脚的自举选项(以启用 RMII 从模式)、因为数据表中未明确说明此选项。 - 请在为这些布线长度找到合适的端接值时提出建议、如果有建议(端接电阻器除外)、请提出其他建议。

- 我们没有得到任何有关 PHY 芯片的勘误表。 也请在这方面提供帮助。

此致、

Madhusoodana Bairy