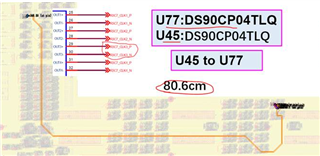

我们的项目中使用了许多 TI DS90CP04时钟驱动器、最长的拓扑如下:U77发送器和 U45接收器都使用 DS90CP04芯片:

最长的 CLK 长度为80.6cm、 对于此类链路拓扑、需要支持的最大时钟频率为700MHz、我们存在以下问题、需要您的大力支持。 谢谢你

DS90CP04芯片在700MHz 时钟频率下支持的最大链路长度是多少? 是否有来自 TI 的任何测试数据?(我们的设计链接太长。 我们如何识别设计风险?)

我们有哪些方法来评估 DS90CP04芯片链路拓扑的可靠性?

3.n TI 官方网站上 DS90CP04芯片的 IBIS 模型、在仿真过程中连接驱动器端后的反射尤其大。 使用 DS90CP04芯片运行 CLK SI 仿真以评估链路长度时、我们应该注意什么? (仿真频率为700MHz)

DS90CP04的输入/输出是在内部进行物理交换还是重新驱动?