主题中讨论的其他器件: LSF0101、 2N7001T、 TXU0101、 SN74LVC1G07

您好、E2E 专家、

你好。

请分享 TCA5405的内部结构、以了解所连接的推挽电平转换逻辑中下拉电阻器的值。 数据表非常详细。

e2e.ti.com/.../translated_2D00_push_2D00_pull.zip

提前感谢您。

此致、

CSC

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、E2E 专家、

你好。

请分享 TCA5405的内部结构、以了解所连接的推挽电平转换逻辑中下拉电阻器的值。 数据表非常详细。

e2e.ti.com/.../translated_2D00_push_2D00_pull.zip

提前感谢您。

此致、

CSC

CSC、

进一步解释 Clemens 的答案

VCC = 3.3V

VIL (最大值)= 0.3 * VCC = 0.3 * 3.3V = 0.99V

为了将 DIN 拉至低于逻辑低电平(VIL)的最大电压输入、您需要一个电阻< VIL (max)/I (I)= 0.99V/0.1uA = 9.9Mohm。

选择一个电阻器、该电阻器小于9.9Mohm、并且还满足 DIN (1MHz 至10kHz)的最小和最大开关频率。 电阻越大= RC 越大=下降时间越长。 如果下降时间过长、DIN 上的电压现在可能有足够的时间下降到低于逻辑低电平、然后再重新切换。

为了简单起见、10千欧姆电阻将正常工作、正如 Clemens 所建议的那样。 我想我会对他是如何到达这里做一些解释。

此致、

Tyler

您好、Tyler、

你好。

问题的一部分是,这种逻辑是否起作用,而这不能通过只知道电流来判断。 我链接的 TT CS1218413显示"如果使用外部10k、您可能会看到更多电流消耗。" 您现在提供这些10k。 此外、该票证上说"用于打开内部振荡器的 DIN 上的第一个下降沿"、这在设计的推挽电平转换中并不是一个非常明确的声明。 例如、当 MCU 未发送时、电平将为低电平。 这是否意味着 IC 端口将进入默认状态?

因此、我想清楚地了解正确的 IC 电源序列以及10k 至 GND 是不会导致不必要的输出开关(例如、当 MCU 未在传输时)或泄漏的正确解决方案。

此致、

CSC

TCA5405的 DIN 输入不得悬空。 因此、对于这款双晶体管级转换器、您始终需要一个下拉电阻器。

TCA5405在其输入端检测到一个高到低边沿时激活。 (因此空闲状态应为高电平。) 如果1.8V 的上电时间晚于3.3V、则 DIN 输入最初将为低电平。 我不知道 TCA5405是否在启动时输入为低电平的情况下检测到边沿。

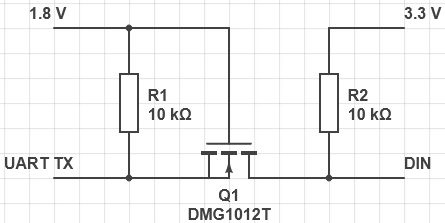

您可以使用2N7001T、TXU0101或 LSF0101等集成电平转换器替换此电路、但也可以使用单个 N 沟道 MOSFET 构建同相转换器:

(此电路不依赖于电源定序、并且在 MCU 禁用时输出高电平。 使用在1.8V 电压下工作的任何 MOSFET。)

您还可以使用 SN74LVC1G07等开漏缓冲器替换 Q1。

CSC、

[引用 userid="480323" URL"~/support/interface-group/interface/f/interface-forum/1185538/tca5405-internal-structure-of-tca5405-pd-for-din/4476825 #4476825"] TT CS1218413我已链接我在线程中或提供的 ZIP 文件中看不到该票证。 是否可以在下一个回复中重新链接? 我认为这里可能缺少一些信息来帮助解决您的问题。

请告诉我 Clemens 的回答是否以任何方式有所帮助。

此致、

Tyler

您好、Tyler、

你好。

您可以忽略 TT 编号。

以下是客户提供的其他信息:

使用推挽的原因是 IC 在 EMI/EMC 方面完全不好。 上拉电阻比直接通过电压下拉电阻器最差。

1.8V 是从3.3V 创建的、因此是的、它会在以后出现。

当我们的电路也禁用 MCU (Hi-z)时输出高电平、不是吗?

请阐明您在使用推挽转换逻辑的电源序列时遇到了什么问题。 您的回答不是很清楚。

抱歉、我不确定写入"输出高电平"时的含义。

是的、由于 DIN 上的 PD、使用此推挽转换逻辑禁用 MCU (output1_MCU 上为高阻态)时 DIN 将为低电平。 您认为这是个问题吗? 到底是什么? 它是否会导致 Q0-Q4端口复位?

然后、可以选择将 pu 从1.8V 放置到 output1_mcu、从而在 MCU 禁用时保持栅极通电并打开 VTT2A

此致、

CSC

CSC、

[引用 userid="480323" URL"~/support/interface-group/interface/f/interface-forum/1185538/tca5405-internal-structure-of-tca5405-pd-for-din/4481179 #4481179"]使用推挽的原因是 IC 在 EMI/EMC 方面完全不好。 上拉电阻比直接通过电压下拉电阻器最差。[/quot]客户运行 IC 的频率是多少? 我很感兴趣、因为建议的最大工作频率小于1MHz。 我感到惊讶的是、客户系统在这种频率下受到 EMI/EMC 效应的影响。

[引用 userid="480323" URL"~/support/interface-group/interface/f/interface-forum/1185538/tca5405-internal-structure-of-tca5405-pd-for-din/4481179 #4481179"]从3.3V 创建的1.8V、是的、它会在以后出现。[/quot]我知道、在您的电流电路中、1.8V 电源的电压较晚、因为它是从3.3V 电源转换而来的。

[引用 userid="480323" URL"~/support/interface-group/interface/f/interface-forum/1185538/tca5405-internal-structure-of-tca5405-pd-for-din/4481179 #4481179"]

当我们的电路也禁用 MCU (Hi-z)时输出高电平、不是吗?

请阐明您在使用推挽转换逻辑的电源序列时遇到了什么问题。 您的回答不是很清楚。

抱歉、我不确定写入"输出高电平"时的含义。

[/报价]我对这种解释中的某些部分感到困惑、但我会给出最好的回答。

如果您的系统以3.3V 电压供电、而1.8V 电源晚了、那么 DIN 将会浮动一段时间。 如果1.8V 接近0V、则底部 FET 将为高阻态、这意味着顶部 nFET 的栅极电压为3.3V、这意味着顶部 FET 关闭。 这意味着 DIN 悬空、除非有一个上拉/下拉电阻器可用于对 DIN 处的电压进行偏置。

最好不要让 DIN 引脚悬空。 此外、当 VCC 未完全上电时、请勿对 DIN 施加电压。

[引用 userid="480323" URL"~/support/interface-group/interface/f/interface-forum/1185538/tca5405-internal-structure-of-tca5405-pd-for-din/4481179 #4481179"]是的、当使用此推挽转换逻辑禁用 MCU (output1_MCU 上为高阻态)时、由于 DIN 上的 PD、DIN 将处于低电平。 您认为这是个问题吗? 到底是什么? 它是否会导致 Q0-Q4端口复位?[/报价]DIN 上的 PD 旨在使 DIN 在器件启动时保持已知状态(逻辑低电平)。 最佳做法是防止 DIN 悬空。 我认为 PD 不是问题。

当一个 POR (上电复位)条件被满足时、复位 Q0-Q4。 该电压电平大约为1V。 如果您需要器件复位、请先断电至 GND、然后再重新加电至 VCC 以成功复位。

[引用 userid="480323" URL"~/support/interface-group/interface/f/interface-forum/1185538/tca5405-internal-structure-of-tca5405-pd-for-din/4481179 #4481179"]我不知道在1.8V 至 output1_MCU 之间添加 pu 如何以不同的方式影响电路的结果、因为1.8V 的电压晚于3.3V 电源供电。 我认为 DIN 下拉电阻器仍需要正常运行。

此致、

Tyler

您好、Tyler、

你好。

>> IC 的工作频率是多少? 我们之所以感兴趣、是因为建议的最大工作频率小于1MHz。 我们感到惊讶的是、您的系统在此类频率下会受到 EMI/EMC 影响。

这不是关于我们的系统、而是关于您的 EVB。 我们在 EVB 上评估您的 IC 时遇到的所有问题。 它可以从"手的魔力"切换-您将手从 PCB 移入10cm、并触发端口。 具有专有单线协议且没有任何保护功能的 IC 是可以预料的(与 I2C 不同)

>>最好不要让 DIN 引脚悬空。 此外、当 VCC 未完全上电时、请勿对 DIN 施加电压。

这意味着、任何设计的唯一解决方案都是该引脚上的 PD! 总是! 因为它是一个环路:当 VCC 未出现时、您应该如何在 DIN 上使用 PU 来保持其在 VCC 上电期间不悬空、同时在该引脚上使用零? 哪种电源序列可以满足此逻辑? 无。 因此、PD 是当时任何设计的唯一解决方案。 逻辑?

>>我们看不到将 pu 从1.8V 添加到 output1_MCU 将如何影响电路的结果

具体取决于:

>>我认为 PD 不是问题。

如果您认为 DIN 到 GND 不会重置 Q0-Q4状态、则是、不需要来自1.8V 的 PU。

我期待您的答复。

此致、

CSC

。

TI-CSC、

[引用 userid="480323" URL"~/support/interface-group/interface/f/interface-forum/1185538/tca5405-internal-structure-of-tca5405-pd-for-din/4486688 #4486688"]这不是关于我们的系统、而是关于您的 EVB。 我们在 EVB 上评估您的 IC 时遇到的所有问题。 它可以从"手的魔力"切换-您将手从 PCB 移入10cm、并触发端口。 具有专有单线协议且没有任何保护功能的 IC 是可以预料的(与 I2C 不同)我假设器件在频率规格内使用。 我从过去使用该器件的过程中了解到、它可能会在 EMI 暴露较高的环境中出现问题、从而在 DIN 上触发不必要的低电平、从而导致输出错误。

[引用 userid="480323" URL"~/support/interface-group/interface/f/interface-forum/1185538/tca5405-internal-structure-of-tca5405-pd-for-din/4486688 #4486688]\n 这意味着任何设计的唯一解决方案都是该引脚上的 PD! 总是! 因为它是一个环路:当 VCC 未出现时、您应该如何在 DIN 上使用 PU 来保持其在 VCC 上电期间不悬空、同时在该引脚上使用零? 哪种电源序列可以满足此逻辑? 无。 因此、PD 是当时任何设计的唯一解决方案。 逻辑?[/报价]抱歉。

回到您原来的问题、您是否仍在尝试确定 附加的推挽电平转换逻辑中的下拉电阻值、或者是否需要回答其他您关注的问题?

此致、

Tyler