您好、专家、

我的客户正在使用 SN65MLVD206、有一个问题需要您的帮助。

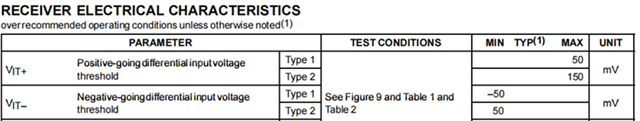

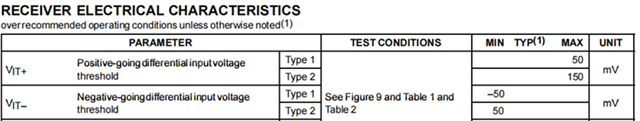

对于有源 正向差分阈值、类型2中的 Vin+为150mV。 如果我们在输入中遇到实际信号、则会出现压降。 我们的正电压阈值是多少、仍然是150mV 或更高?

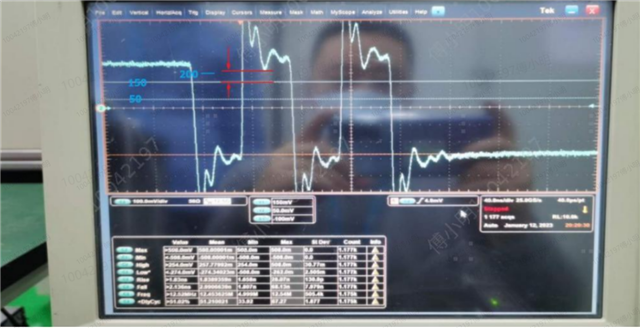

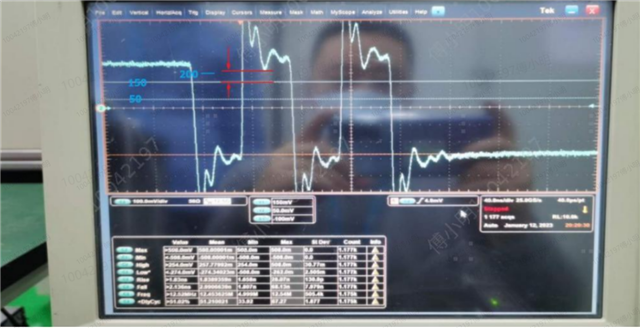

请将此输入波作为参考。

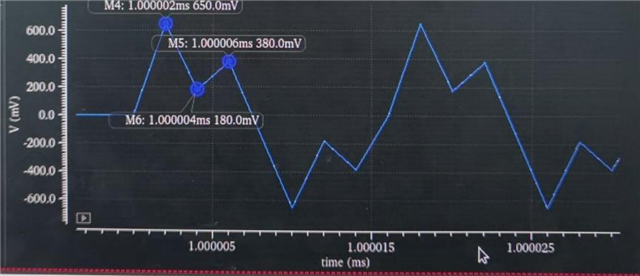

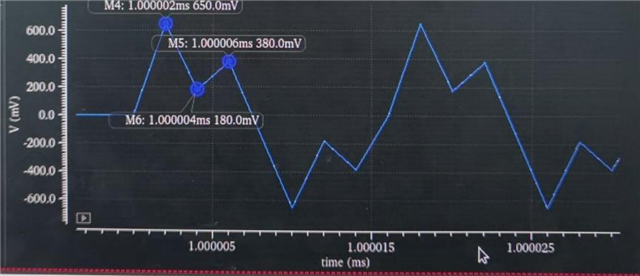

这第二张图片显示信号从650mV 下降到180mV、然后回到380mV、这180mV 下降将使输出电平相反或不相反?

BR

CHI

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、专家、

我的客户正在使用 SN65MLVD206、有一个问题需要您的帮助。

对于有源 正向差分阈值、类型2中的 Vin+为150mV。 如果我们在输入中遇到实际信号、则会出现压降。 我们的正电压阈值是多少、仍然是150mV 或更高?

请将此输入波作为参考。

这第二张图片显示信号从650mV 下降到180mV、然后回到380mV、这180mV 下降将使输出电平相反或不相反?

BR

CHI