主题: TCA9517-Q1中讨论的其他器件

团队、

客户计划 在其应用中使用 TCA9548A-Q1、并考虑控制器 MCU SDA/SCL 负载电流的一些最坏情况。

场景:

--> 1个输出通道激活在快速模式,3.3V 上拉

-->所有8个输出通道均 在快速模式下激活,3.3V 上拉

共有两个问题:

1.如何计算控制器和输出通道两侧的拉电阻,以确保两种情况都能正常工作? (我曾尝试使用 I2C 设计器工具、但在那里找不到 TCA9548。)

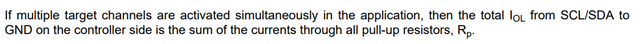

TCA9548A-Q1 数据表中说:

这对 MCU 控制器 SDA/SCL 引脚电流能力意味着什么?

您能帮助计算 MCU 控制器需要支持的电流吗?

如果此电流超出 MCU 控制器的功能范围、该怎么办? 您能推荐任何 I2C 汽车缓冲器 IC 来帮助吗?