1 μ A、状态检测配置、这些配置用于哪些状态?

2、如何理解这里的内容? 这种2.0代低速的最终工作原理是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

1 μ A、状态检测配置、这些配置用于哪些状态?

2、如何理解这里的内容? 这种2.0代低速的最终工作原理是什么?

尊敬的艾文:

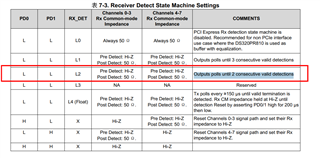

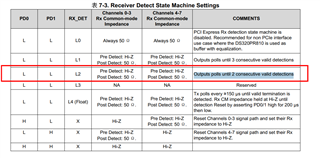

1.这些配置均适用于 PCIe 应用。 所有情况之间的主要区别是 rx_det 生效之前所需的检测次数。 另一种情况是适用于非 PCIe 应用、其中我们的器件用作缓冲器。 这取决于您希望检测的速度。

2.我不是在关注你在这里问的问题吗? PCIe 第3代及第3代链路通过一个称为链路均衡的过程、该过程本质上将根复合体(RC)与端点连接起来。

有关 PCIe 中链路训练的更多信息、请参阅此应用手册: www.ti.com/.../snla415.pdf

此致、

Vicente.

尊敬的艾文:

与 PCIE gen5相比、PCIE gen1 & 2损耗预算更大(假设无信号调节为36DB)。 最终、由于传输所需的距离太远、数据速率也变得如此之快、所以引入了信号调节器的理念。

所有较新的 PCIe 设备 必须 将按照规范向后兼容 PCIe gen1.0和2.0。 所有 PCIe 链路都始于 gen1、在转换到更高的数据速率之前、gen1是最低且最基本的数据速率。

PCIe 1.0 2.0的规范已有20年和16年的历史。 我们没有这方面的参考设计。

我不是在关注你们的问题。 我知道正在使用 DS320PR810。 问题是它只设法建立第2代链路而不是第5代链路吗? 我也不明白您所说的"将识别8个器件"是什么意思、请详细说明一下...

请阅读随附的应用手册第5和第6页。 它介绍了 PCIe Gen1/2链路训练的发生方式。 PCIe 第3代及以上版本需要链路均衡、但所有 PCIe 链路都要经过链路训练。

此致、

Vicente.

尊敬的艾文:

如果客户只看到第2代链路而不是第5代链路、从而落入 x8或 x2之手、则很可能客户使用了不正确的 CTLE 设置、从而过度均衡。

我建议减少 CTLE、并使用示波器观察任何异常情况。 如果客户具有 Tx 符合性测试方法、则可以使用 Tx 符合性测试来完成。

PCIe 协议协商始终从第1代开始。 客户是否每次都生成到 Gen1全长?

如果可能、我建议尝试不同的 RC 和 EP、以查看是否出现相同的行为。

此致、

Vicente.