主题中讨论的其他器件: USB2ANY

嗨、Nicholaus:

您能帮助查看更新后的原理图和布局吗?

设计材料

https://txn.box.com/s/l2k78zg4w4pn9wvdmv7kh3yxspsgo0

感谢您的帮助!

之前是 E2E 帖子

Br、

Scott

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

嗨、Nicholaus:

您能帮助查看更新后的原理图和布局吗?

设计材料

https://txn.box.com/s/l2k78zg4w4pn9wvdmv7kh3yxspsgo0

感谢您的帮助!

之前是 E2E 帖子

Br、

Scott

Scott、您好、

客户觉得我对电源的建议只是跟在后面、没有做其他推荐的更改。 我将跟进布局审查。

高速差动 I/O

PET: TX 侧0.22uF 耦合电容

根据: 好、RX 侧没有电容器。

参考时钟

REFCLK: 连接至 PI6CB33201 PCIe 时钟缓冲器

REFCLK_OUT: 悬空

JTAG

TDI: 悬空

TDO: 悬空

TMS: 悬空

TCK: 悬空

TRST#: *悬空、如果不使用、建议1K 至 GND。 系统噪声可能导致意外的故障。

执行微步进

ICC_1: 悬空

ICC_2: 悬空

ICC_3: 悬空

RX_DET_BYP: 20K 至 GND、自动 RX 检测

宽度: 浮动、1x8链路宽度。

PCI-Express 辅助信号

CLKREQ#: *100K 上拉至1.8V。 默认情况下 CLKREQ#取消置位。 假设 EGPU 将拉低该电平以避免 L1.1状态。

PERST#: 由 EGPU 控制。

PRT1_RST#: *悬空、建议将 R0417上拉至1.8V。

PRT0_RST#: *悬空、建议将 R0415上拉至1.8V。

系统管理总线

模式: 悬空、链路宽度管理器;EEPROM > 16k 位

SMBCLK: *未显示连接。 确保有一个4.7K 上拉至3.3V 的电阻器。

SMBDAT: *未显示连接。 确保有一个4.7K 上拉至3.3V 的电阻器。

SMB_ADDR_0: 1K 至 GND

SMB_ADDR_1: 1K 至 GND

* SMB_ADDR = 0x20、EEPROM 读取器和链路宽度管理器

EE_CLK: 具有2K 个上拉电阻器、连接到1.8V、并连接到16K EEPROM

EE_DAT: 具有2K 个上拉电阻器、连接到1.8V、并连接到16K EEPROM

增强

好的、使用铁氧体磁珠分离了数字电源和模拟电源、如 EVM 原理图中所示。 必须确保1.17V 电源轨始终处于1.17V 的2%以内。

此致、

尼古拉斯

有一封华硕电子邮件,我被环入. 在此处添加注释以供将来参考:

TRST 编号: *悬空、如果不使用、建议将1K 接地。 系统噪声可能导致意外的故障。

[TIM]我们将填充 R0422。

CLKREQ#: *100K 上拉至1.8V。 默认情况下 CLKREQ#取消置位。 假设 EGPU 将拉低该电平以避免 L1.1状态。

[Tim]是的。 EGPU 会将此下拉为低电平以退出 L1.1状态。

PRT1_RST#: *悬空,建议将 R0417上拉至1.8V。

PRT0_RST#: *悬空,建议将 R0415上拉至1.8V。

[Tim]好的。 我们将安装 R0417、R0415。

SMBCLK: *未显示连接。 确保有一个4.7K 上拉至3.3V 的电阻器。

SMBDAT: *未显示连接。 确保有一个4.7K 上拉至3.3V 的电阻器。

[Time]在第5页。 抱歉、忘记将此页放入原理图了。

Scott、您好、

我正在运行仿真、以便了解我能否提供任何更多特定于设计的示例、但目前客户可以继续添加我之前要求的布局更新。 似乎他们解决了对内偏移问题、但没有解决我提到的其他问题。 我还添加了新建议、即按照 信号调节器高速指南中的说明在 Tx 电容器下添加空隙。

过孔:

背钻:请确保对顶部 IN1或底部 IN3之间的所有高速过孔进行背钻、以便不会如 信号调节器高速指南 文档中第4.6节所述创建残桩

接地过孔:在高速信号过孔附近添加接地过孔、以确保一致的接地和最小的阻抗变化、如 信号调节器高速指南的图10所述

跟踪:

对内偏移: 好的、所有 PCIe 高速通道的所有布线都相差<5mil。

电容器下方空洞:在电容器下添加 GND 空洞

此致、

尼古拉斯

王文信

好的、这很好、重定时器不会出现任何问题、也支持这种时钟拓扑。 请参考我们的高速设计指南、并在方便时进行以下更改。

过孔:

背钻: 请确保对顶部 IN1或底部 IN3之间的所有高速过孔进行背钻、以便不会如 信号调节器高速指南 文档中第4.6节所述创建残桩

接地过孔: 在高速信号过孔附近添加接地过孔、以确保一致的接地和最小的阻抗变化、如 信号调节器高速指南的图10所述

跟踪:

对内偏移: 好的、所有 PCIe 高速通道的所有布线都相差<5mil。

电容器下方空洞: 在电容器下添加 GND 空洞

此致、

尼古拉斯

尊敬的 Nicholaus_Malone:

两个问题。

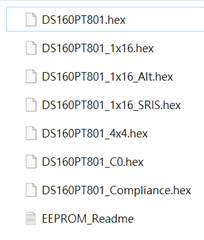

1.我得到了 Scott 的 EEPROM 映像。 这是 SMT 之前预加载的 EEPROM 映像吗? 这意味着我可以在 SMT 之前通过 EEPROM 编程插槽使用此图像(Hex 文件)对 EEPROM 进行编程?

2. 我似乎需要通过 SigCon Architect 配置 DS160PT801。 但我找不到任何 DS160PT801配置文件或更新程序。 从何处可以获取 DS160PT801更新程序?

谢谢。

Scott、您好、

如果客户未遵循建议的布局更改、并且无法实现第3代/第4代、则可能是信号完整性问题。 但是、GPU 应自动降至 PCIe 第1代、并在设备管理器中看到该器件。 我认为 BIOS 更改不会产生重大影响。

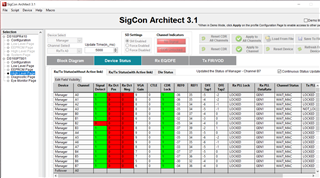

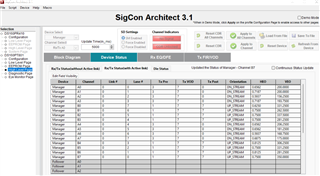

请先截取 SigCon Architect 的高级页面屏幕截图后开始。

此应用中的电缆长度是多少? 如果您使用较短的电缆、结果是否会发生变化?

谢谢。

尼古拉斯

Scott、您好、

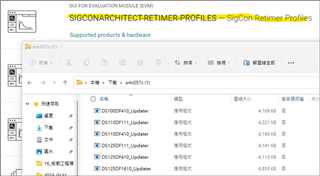

可回答您的电子邮件问题。 DPS 软件狗最终转换为 USB2ANY、其网址为:USB2ANY Evaluation board | TI.com

有关如何使用 SigCon Architect 的第二个问题。 有关如何使用 SigCon Architect 的说明、请参阅 DS160PT80X16EVM。

如果客户希望将 SigCon Architect 与自己的定制电路板一起使用、则需要获得如上所述的 USB2ANY 并将其连接到 SCL/SDA I2C 线路。 之后、该过程将与 EVM 相同。 如果您需要帮助、请告诉我。

此致、

尼古拉斯

嗨、 Nicholaus:

1.高级页面屏幕截图。 看起来像一些通道损耗信号?

2.电缆长度约为16英寸。

嗨、Nicholaus:

将"交叉选项"从1x16调整为1x8、然后点击"初始化"按钮。 重新启动系统后、它将 成功到达 DS160PT801。 Nvidia 显卡驱动程序也出现在设备管理器中。

但我不知道为什么 交叉选项显示系统为1x16。 我们是否可以从 Low Level Page 或 EEPROM 页面读取任何寄存器来查看链路宽度设置是否正确?

此外、我还从系统捕获了一些可成功实现 PCIe 第4代链路的图像。 我们有一些问题。

1. VGA 增益是什么意思? VGA 增益是否与预加重相同?

2.根据图像,PCIe 信号是否正常? 我们是否需要修改任何设置以提高 PCIe 信号质量?

谢谢。

王文欣

系统重新启动后、很可能寄存器已复位、并且链路宽度设置"1x8"改回"1x16"。 如果链路成功建立、则表明没有问题。 我不确定为何 在您执行此更改时开始起作用。

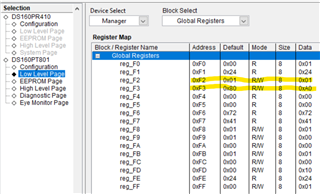

是的、您可以查看 MySecure 上的配置指南中的寄存器映射。 它将向您显示0xF2和0xF3是链路宽度寄存器。

1. VGA 增益是一种可变增益放大器,出现在重定时器的 Rx 上,它自动适应最佳设置,不应更改。 它与发射前的技术不同、后者是一种 Tx 信号调节技术。

2.外观不错,但最好是进行 PCIe 系统测试,以确保信号质量好。 重定时器只能显示重定时器中的信号质量、而不能显示根复合体或端点附近的远端信号质量。 重定时器会自动将 其所有信号调节设置调整为理想值、因此无需像转接驱动器那样修改其设置。

另外、他们使用的似乎是 SigCon Architect 3.1。 MySecure 文件夹中的版本是 SigCon Architect 3.2。 我建议客户更新到最新版本。

此致、

尼古拉斯

嗨、 Nicholaus:

1.我捕获了有关0xF2和0xF3寄存器数据的图像、系统上电。 链路宽度为 x16。 但它很奇怪。 EEPROM_Readme 文件指出、链路宽度由"宽度"引脚设置决定、而我们的"宽度"引脚是悬空的、因此应该是 x8链路宽度。 不清楚为什么它成为 x16链路。

重定时器如何确定链路宽度? 链路宽度是否不仅取决于宽度引脚?

2.是否可以通过 Sigcon Architect 修改 EEPROM 数据以强制链路宽度为1x8?

1.正确。如果使用 DS160PT801.hex 文件、不将链路宽度设置加载 到0xF2或0xF3寄存器中、则链路宽度设置应与引脚搭接设置无关。 根据数据表、浮动链路宽度引脚不是1x8。 这是寄存器默认设置、为1x16。 您是否有最新的数据表?

如果宽度引脚悬空、则链路宽度设置按顺序确定:

1. 0xF2和0xF3中的默认寄存器设置应为1x16。

当前寄存器设置、无论是由 EEPROM 加载还是通过 I2C 手动更改。

当链路宽度引脚悬空时、可以通过两种方法将链路宽度强制为1x8:

1.在 EEPROM 映像中将0xF2和0xF3寄存器设置为1x8。

2.在 PCIe 链路训练开始之前、向0xF2和0xF3寄存器写入一个1x8的链路宽度。

您还可以将引脚搭接设置更改为3级(10K 至 PWR_1)、从而将链路宽度强制设置为1x8。

此致、

尼古拉斯

嗨、 Nicholaus:

另一个问题。

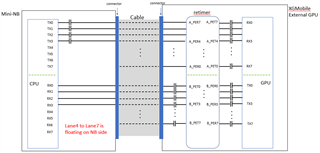

到目前为止、x8模型是正常的。 但是、当使用同一个外部 GPU 设备连接到 x4笔记本电脑时、这是异常的。 症状与之前相同。 GPU 未出现在设备管理器中。

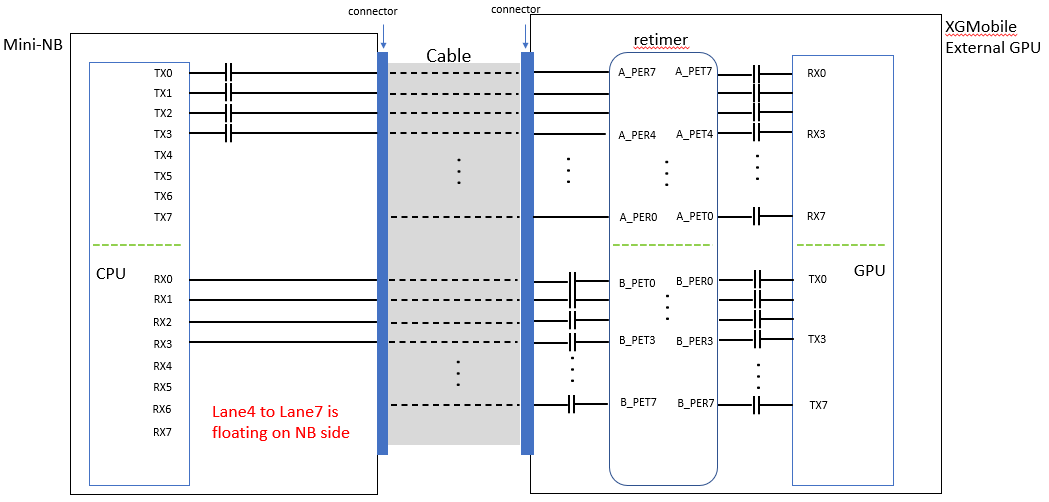

拓扑如下所示。

我的问题是:

1.重定时器是否支持1x4模式? 根据数据表、我只能看到它支持2x4。

2.我已经尝试从 Sigcon Architect 将"Bifurcation Option"修改为1x4和2x4,但仍然无法解决此问题。

3. 我已经尝试将 strap 引脚设置修改为1级 、但仍然无法解决此问题。

4.根据拓扑。 我应该设置哪个链路宽度设置? 1x4或2x4?

尊敬的 David:

配备 x4笔记本电脑的 x8模式下、设备管理器中会显示外部 GPU。 看起来该问题通过将重定时器更改为1x8模式来解决。

但 GEN 速度仅为 PCIe 第1代。 不确定正在发生什么、因为使用 x8笔记本电脑时、GEN 速度可以达到 x8模式的 PCIe Gen3。

我从 Sigcon Architect 那里捕获了一些图像。 您能帮助检查吗?

Thanls

尊敬的 Wen-Hsin:

我认为、由于在四个通道 A/B4-7上检测到 RX 终端、链路能够进入第1代合规性模式。 如果记住正确的话(根据下图)、所有通道 A4-A7和 B4-B7都将进行端接、而通道 A0-A3将进行未端接。 据我所知、在 x4模式下、重定时器查找通道0-3上的端接和信号、而不是通道4-7。 在 x8模式下、重定时器会在通道4-7上检测4个通道的活动流量、并开始在这些通道上传输合规模式、而使通道0-3空闲。