Other Parts Discussed in Thread: DP83867IR

你(们)好

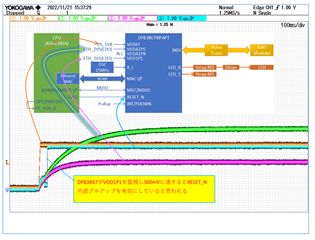

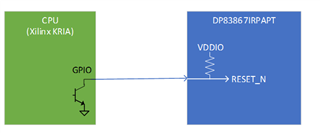

我的客户与 DP83867IR 的连接不稳定、下面列出了问题说明

| 情况 | 该设计的链接 | 事件 | 注意 |

| 1. | 在连接以太网集线器和 LAN 电缆的情况下启动时、链路偶尔会失败 | 影响 | |

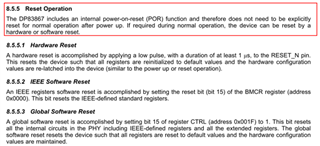

| 2. |

移除 RESET (RESET-N 引脚)信号后、连接到 LED_0的 LED 会亮起 |

很少 | 这种情况下没有链路 |

| 3. | 所有 MDIO 读取返回1 (DP83867 无响应) | 很少 | 这种情况下没有链路 |

| 4. | MDIO 读取返回意外值 | 很少 |

这种情况下没有链路 返回相同的值、直到电源复位 |

| 5. | RESET (RESET-N)不起作用 | 很少 | 这种情况下没有链路 |

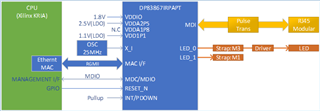

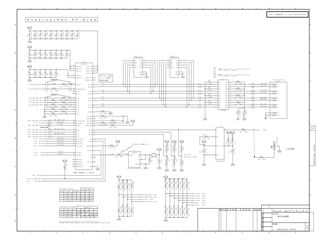

方框图和电路如下所示

您能否建议可能导致此问题的原因以及解决方案?

此致