您好!

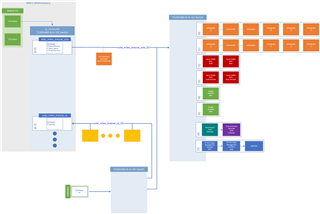

对于多个 I2C 开关、有人提到、如果路径中有多个开关、我们需要注意 I2C 的 VIL。 我与答案混淆、因为只有一个器件能够应答主器件、这意味着在 与主器件通信时、只有一个从器件置位为低电平。 为什么我们应该在 I2C 线路上的电流限制处于低位时担心呢? 您能解释一下吗? 我想将三个 I2C 开关与 两个开关串联、这两个开关连接到 各自下游通道上的多个从器件、如下所示。 我是否需要担心 下面电路图中的总电容和驱动器强度等任何问题? 仅供参考、第三个开关仅用于隔离另一个主器件。

此致

夸伊斯