主题中讨论的其他器件: DS250DF210、 DS250DF810、 DS280DF810、DS250DF230

大家好、

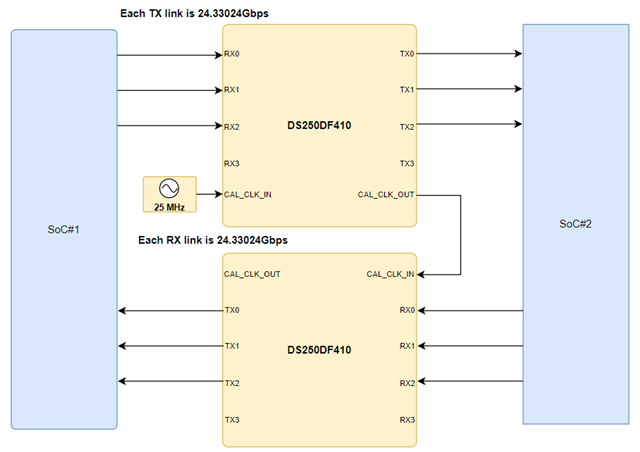

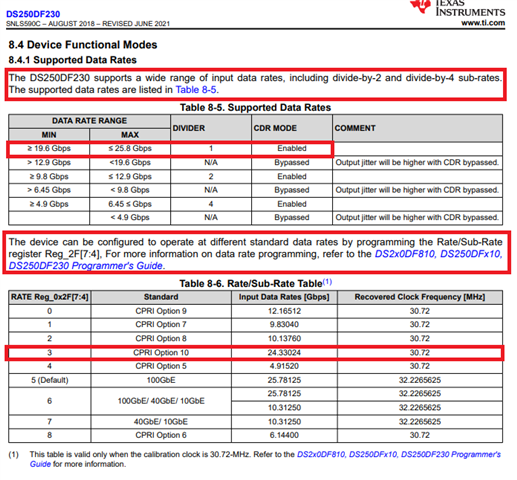

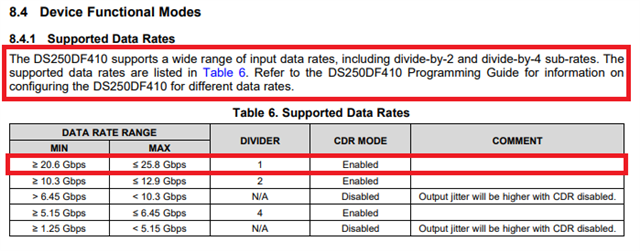

由于电路板上的 PCB 布线长度(~23英寸)、我们正在考虑将 DS250DF410ABMR 用于24.33024Gbps 接口(请参阅参考编号1)。 在比较 DS250DF230 与 DS250DF410时 、我们发现该数据速率是数据表中专门提及的标准数据速率之一(请参见下面的参考编号2)。 但是、DS250DF410数据表未提及相同之 处、仅 指定了≥20.6Gbps 至≤25.8Gbps 的范围(请参阅下面的参考编号3)。

此外、在 DS2x0DFxx0_SNLU182G_Programmers_Guide 中、提及的 DS250DF410子速率的标准子速率不包括24.33024Gbps (表7-6. DS280DF810、DS250DF810、DS250DF410、DS250DF210标准速率模式可通过 ReG_0x2F 进行配置)。 另外还提到、如果数据速率范围在 VCO 范围内、我们可以手动设置数据速率(请参阅下面的参考编号4)。

查询:

1) 1)我们可以将 DS250DF410用于24.33024Gbps 吗? 我们是否需要注意任何特殊事项(配置、CAL_CLK 等) 原因是什么?

2) 2)对参考#1中显示的框图有任何评论?

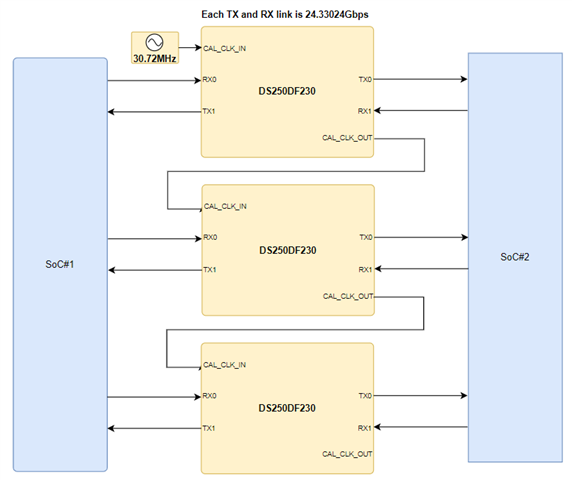

3) 3) 对于此应用、是否首选提供2数量的 DS250DF410 (如参考编号1所示)或3数量的 DS250DF230以及30.72MHz CAL_CLK (如参考编号5所示)? 请检查并注释参考#5中显示的方框图。 请告诉我您的想法。

参考#1:实施方框图

参考2:DS250DF230 数据表 、其中提到了24.33024Gbps 的支持

参考#3: DS250DF410 数据表中支持的数据速率表

参考#4: DS2x0DFxx0_SNLU182G_Programms_Guide 中的"手动数据速率设置"部分

参考#5:DS250DF230的实施方框图