您好!

我们的电路板包含一个 FPGA 和 一个 带 SFP 的 DP83869HM PHY (RGMII 至1000Base-X)。

启动时、PHY 始终正常启动。 但重新编程 FPGA 后、有时 PHY 不响应 SMI 总线。

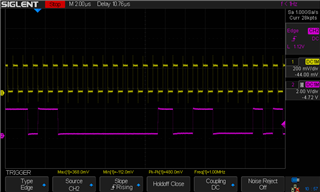

MDIO 读取时、我总是会获得相同的数据(第一个数据是随机数据、所有下一个数据与第一个数据相同)。 PHY 似乎已冻结。

只有下电上电才能起作用。 XI 时钟和复位信号通过下拉电阻器从 FPGA (硬编码、不可控制)传出。

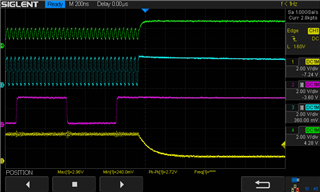

一些时序测量:

- XI 时钟在 HW_RESET 上升沿之前的17ms 启动。

- MDC 时钟持续运行,在 HW_RESET 后34us 启动。 频率为1MHz。 (第一次 MDIO 操作需要很长时间)。

提前感谢、

雅各布