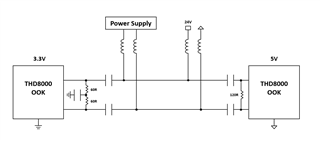

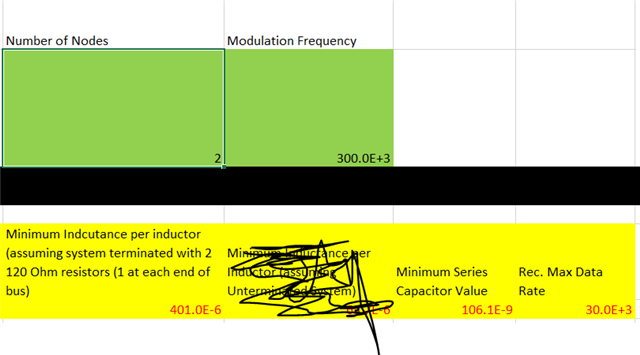

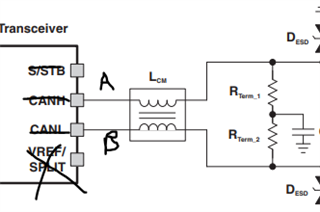

主题中讨论的其他器件: THVD8010

℃内容是关于在-40 μ s 下执行 OOK 操作、我们需要技术支持。

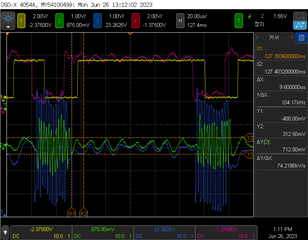

以下两个波形是从一个通信数据包测得的。

|

|

|

1.异常波形 |

2.正常波形 |

波形说明

黄色:主器件 Rx、绿色:主器件 A-B、红色:从器件 Tx、蓝色:从器件 A-B

支持请求是在开关键控(500kHz)之后的振荡部分(58kHz 和104kHz)进行错误操作和正常操作。

- 请求技术支持、以了解在58kHz 下进行错误操作的原因。

- 请求技术支持、以了解在104 kHz 下正常运行的原因。