Other Parts Discussed in Thread: TLK10081

您好!

我们已经完成相应设置、将8x625 Mbps 链路聚合为1x5.00 Gbps 链路。 我们仅在 TX 模式下使用 TLK10081。

在数据生成器芯片处于空闲模式时、它会生成0xBC 字符。 我们在通道0上配置了 TLK10081以将此 charackter 替换为0x5C。 这一切看起来都很好、我们在 FPGA 上接收到0xBC 和0x5C 字符。

但是、当我们基于 FPGA 而不是0xBC char 触发(注意、我们已再次在 FPGA 中将0x5C 替换为0xBC)时、我们 偶尔会得到

"6x 0xFE - 4x"idle char"(在本例中为0xFD)- 1x 0xFE"。 这些字符全部标记为控制字符。

我们得到的序列:/K30.7/K30.7/K30.7/K30.7/K30.7/K30.7/K30.7/K30.7/K30.7/K29.7/K29.7/K29.7/K29.7/K29.7/K30.7/

我们的 TLK 配置为:

{ TLK81_GLOBAL_CONTROL, 0x8610 }, // Reset{ TLK81_CHANNEL_CONTROL, 0x0000 }, // Disable link training{ TLK81_HS_SERDES_CONTROL_1, 0x8315 }, // Set PLL multiplier to 8x{ TLK81_HS_SERDES_CONTROL_2, 0xA940 }, /* Set HS TX rate to half rate Disable HS RX */{ TLK81_HS_SERDES_CONTROL_3, 0x1540 }, // Disables high frequency peaking.{ TLK81_HS_TP_CONTROL, 0x0520 }, /* Disable HS Test Pattern (0x2520)(0x2200)(0x2020)(0x0520) Set HS tp 2^7 Set LS PRBS 2^7 Disable Deep Remote Loopback */{ TLK81_LS_SERDES_CONTROL_1, 0x8110 }, // Set LS_MPY to 4 times{ TLK81_LS_CH_CONTROL, 0x0001},{ TLK81_LS_SERDES_CONTROL_2, 0xDE02}, /* Set LS PLL to quarter rate Disable LS_RX_ENTX to turn off LS transmitter*/{ TLK81_CLK_CONTROL, 0x0080 }, // CLKOUTxP/N disable{ TLK81_HS_ALIGN_CODE_CONTROL, 0x02BC },// Set TX marker selection on lane 0{ TLK81_HS_CH_CONTROL, 0x0880 }, // Enable TX marker replace { TLK81_EXT_ADDRESS_CONTROL, TLK81EXT_VS_TX_MARKER_REPLACE_CHAR },{ TLK81_EXT_ADDRESS_DATA, 0x25C }, // TX replace char 0x25C{ TLK81_EXT_ADDRESS_CONTROL, TLK81EXT_VS_TX_IDLE_P_CHAR },{ TLK81_EXT_ADDRESS_DATA, 0x2FD }, // TX idle Pchar{ TLK81_EXT_ADDRESS_CONTROL, TLK81EXT_VS_TX_IDLE_N_CHAR },{ TLK81_EXT_ADDRESS_DATA, 0x2FD }, // TX idle Nchar{ TLK81_RESET_CONTROL, 0x0008 } // DATAPATH_RESET

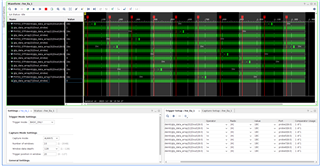

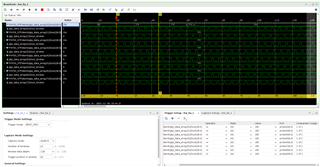

这就是在 FPGA 中执行通道去交错后得到的结果:

我们怀疑时钟容差补偿导致了这种情况。 但是、我们需要单个空闲字符(0xFD)。 那么、为什么它不是一个0xFD 字符、为什么我们也会得到几个0xFE 字符?

提前感谢。

亚历山大~