Other Parts Discussed in Thread: TLK6002, CDCM6208

主题中讨论的其他器件: CDCM6208

您好

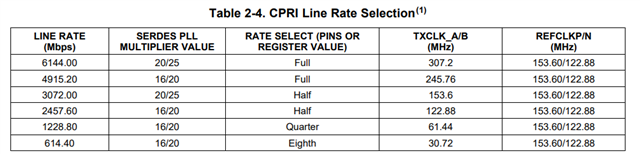

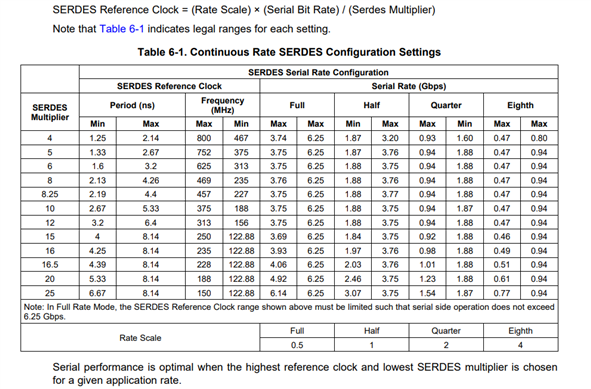

我正在尝试将 TLK6002配置为半速率模式。 我将按照下表选择参考时钟和 SERDES 乘法器。

我将配置串行器/解串器以在其下工作 2.46 Gbps 在 半速率模式 。 根据下面提供的公式和表中确定的乘法器值、我选择了 以下配置。

1.串行速率:2.46Gbps。

2.串行器/解串器 MULTIPLIERR:20

3. TX_CLK=( SerDes_serial_rate/20 )= 123Mhz;

4.通过以下公式、我得到 REF_CLK =123MHz;

当我对上述配置进行编程时、会出现 Transmit Overflow 和 Underflow 错误。

是否需要在计算中进行任何更正?

注意:我已经将0x01寄存器编程为半速率。

谢谢

马利卡朱纳住宿加早餐旅馆