大家好、

在我们测试 THVD8000时、RS 很容易受到干扰。

电流配置为差模、载波速率为2M、并采用抗共模干扰设计。 在最终测试中、RS 的误码率为50%、而在添加了磁环之后仍然是20%。

Question:

1.还有哪些其他方法可以提高这项计划的抗干扰能力?

2.本产品也用于电力和楼宇自动化。 如何实现抗干扰设计?

谢谢!

雷纳

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Rayna:

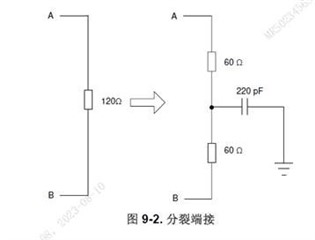

1、因此、除了如上面所示的分裂终端之外、如果担心干扰的话、下一个最常见的附加器件是共模扼流圈。 根据系统设置的不同、也可以使用滤波电容器。 一般而言、我们没有太多看到铁氧体磁珠、但也可以选择使用铁氧体磁珠。

以上是可用于帮助缓解排放问题的一般组件。 但是、由于干扰的原因、位损失可能不是100%、因为系统布局对于正确通信非常重要。 因此、对于问题2的答案、请参阅以下内容:

2.除了增加 EMC 友好元件外,高 SI THVD8000最重要的方面是总线架构+系统布局。

如果您可以提供包含以下信息的原理图、它将帮助我检查总线架构。

主题。 系统中的节点数量。

2b. 数据速率是多少(我知道调制是2MHz -但您要尝试通过什么数据速率?)

2c)总线的时间长度

2d)如果系统中有2个以上的节点-网络拓扑是什么(菊花链目前为止是最好的-从 SI 角度来看、其他一切都将变得更糟)

2E)您在系统中使用哪种类型的电缆?

2f)是否每个通信节点都连接到电源负载或电源节点?

请告诉我有关第2点的问题、以便我能够更好地专门研究此系统。 一般而言:

1.调制频率下共模负载>= 375欧姆

2.串联电容器在调制频率下<= 5欧姆

3.如果系统中有2个以上的节点-它们采用菊花链方式连接;THVD8000的未端接存根长度通常最大为~300mm 至500mm、因此菊花链可将存根长度减少到几 mm、从而防止此处出现问题。

4.电缆具有120欧姆的特性阻抗。

5.端接两个节点(终端节点)(分裂端接或标准端接)

6.最大数据速率<=调制频率的1/10。

7.未端接残桩(对于非终端节点)最大为300mm 到500mm -否则您将得到反射。

这些是最重要的方面-因此如果您可以共享您的原理图(即使它仅针对1个 THVD8000节点(假设其他节点非常相似)) 了解是否遵循了所有基本准则以了解需要改进-因为如果不满足上述条件、我认为 EMC 友好组件不能解决问题。

请告诉我!

此致!

帕克·道德森

您好、Parker、

我附上了原理图和布局供您参考。

客户反馈 UART 通信波特率为230400、通信波特率为每秒400个数据包、每个数据包为12个字节。 将载波频率设置为2MHz (5MHz 抗干扰功能与上述相同)、在 A 和 B 通道之前添加电容器、铁氧体磁珠、共模电感器、三端滤波电容器和磁环无法显著提高 EMC 抗辐射抗干扰和抗传导抗干扰能力。

RS 测试条件:20V/m、80MHz 1GHz。

通信包丢失情况十分严重、在80MHz -240MHz 频段或270MHz -340MHz 频段的干扰下、每秒丢失200多个数据包。

将 RS 测试条件降至12V/m、无有效改善。

CS 测试条件:0.15MHz -80MHz。

数据包丢失情况也很严重、通过添加多个磁环可以有效改善这种情况、最终不会丢失数据包。

总线长度:3.5米、电缆为普通电缆、不能屏蔽。

总共有两个通信节点、一端连接到主机、另一端连接到应用部分。

有没有其他改进抗干扰性能的建议?

e2e.ti.com/.../THVD8000-layout.docx

谢谢!

雷纳

尊敬的 Rayna:

在原理图上有一些注释-由于抗干扰还需要更大的 SNR -这意味着您不能使总线过载-该设计使总线过载。

C19和 C20本身就违反 THVD8000的共模负载-在2MHz 下、它们近似。 142欧姆阻抗-允许的共模负载的绝对最小阻抗为375欧姆。 通过使总线过载、可以大大降低信号强度、任何干扰都会对系统产生大得多的影响。

C13和 C14较差、因为它们位于1nF、因此几乎是 C19和 C20的两倍。

您的电感器太小-在2MHz 和2个节点上、每个节点的有效电感为60.2uH、这是假设没有滤波电容器-使用滤波电容器时、您将需要更多的电感-在一般情况下、滤波电容器是您可以添加的最差 EMC 元件 至 RS /LSF-485、由于共模负载要求-您的客户具有10uH (L1和 L2)-这也是共模负载规格的一部分、因此总共模负载(电感器、滤波电容器、 和其他收发器)必须保持375欧姆或更高的共模阻抗。 在10uH 下-假设没有电源电流降额-每个电感器的电阻约为125欧姆-因此单个电感器就已经使总线过载。

接下来、通过电感器供电的直流电源没有大容量电容-假设有这个电容。 即直流电源需要大容量电容、否则耦合网络将无法正常工作。 2MHz -即使是100nF 或1uF 之类的电容也可能或多或少可以-但需要有一些东西、否则可能会存在干扰问题。

我想说他们使用的数据速率高于我们的建议-在2MHz、我们不建议高于200kbps -因此可能存在大于+/-2%的占空比失真; 然而、这样的较短总线问题也许没有那么大-但是如果他们想消除任何风险、他们需要将调制频率提高到更高的水平(至少10倍数据速率)。

仅就基本原理图而言、该设计很可能不起作用、因此需要进行一些更新。

接下来、我对布局有一些意见-但由于电感器所需的差异、这很可能会改变。

电感器是并联的并且靠近总线-电感器中的电流最好是沿 y 方向流动、而不是沿 x 方向流动、因为现在是这样。 这是因为磁场与电流垂直运行-在电流设置中、这意味着电感器更适合通过其磁场与总线进行耦合。

使用多边形覆铜而不是迹线可以更好地处理两种连接:

在端接部分、是我关心的问题:

用蓝色圈出的项目应改为多边形覆铜。 它们都连接到同一个网络-这种 布局增加了更多拐角、可能导致更高频率能量以及增加电流密度出现问题。 只需铺这些覆铜而不是走线、就可以解决这个问题。

另一个问题是电感器的 GND 连接/THVD8000

在一个相当小的布线上只有两个过孔-最好添加另一个过孔、并稍微加宽布线、以防止过多的接地漂移。

此外、应该校正的迹线上存在不必要的曲线。

我添加了一个设计计算器、以便客户快速确定元件的尺寸。 由于应用程序已终止、请忽略未端接系统的任何复选框(有一小部分系统不需要端接的用例-这不适用于此系统)。

e2e.ti.com/.../7853.THVD80x0_5F00_Design_5F00_Calculator.xlsx

请告诉我他们是否/何时可以完成新设计。

此致!

帕克·道德森