SN65DSI86支持多大的显示分辨率?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

要了解 SN65DSI86是否支持您的显示面板分辨率、需要确定所需的最低 DSI 时钟频率。 DSI86的 MIPI DSI 输入可支持高达750MHz 的频率。

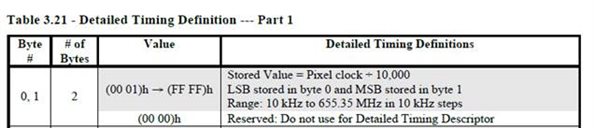

要找到所需的最低 DSI 时钟频率、您需要执行简单计算来确定流比特率。 流比特率显示位传输到显示屏的速率。 要执行此计算、您首先需要找到显示像素时钟频率。 显示屏 EDID 应显示支持的像素时钟频率、它通常位于 EDID 的详细时序定义部分。

例如、在此 EDID 中、135MHz 的像素时钟由十进制的13500表示、存储为 BCH、34h。

如果无法从 EDID 找到像素时钟频率该怎么办? 在本例中、如果您至少知道 Htotal、Vtotal 和所需的刷新率、那么您可以使用以下公式估算所需的 DSI CLK 频率:

执行该计算后、您可以使用像素时钟估算来执行以下流比特率和最小 DSI CLK 公式。 如果无法在显示 EDID 中找到实际像素时钟频率、请仅使用显示像素时钟频率估算。

流比特率是 eDP 显示像素时钟频率和每像素位数(bpp)的函数、如下所示。

假设24bpp 和135MHz 的像素时钟频率、流比特率将为3.24GHz。 流比特率用于计算 DSI86支持所需分辨率所需的最小 DSI 时钟频率。 请注意、DSI86支持的最大 DSI 时钟频率为750MHz。 DSI86最多可支持8个 DSI 数据通道。

流比特率为3.24GHz 且假设使用全部8个通道、则所需的最低 DSI 时钟频率为202.5MHz。 此频率完全处于 DSI86支持的 DSI 时钟频率的750MHz 限制范围内、因此支持该面板。