https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1273106/pca9306-pca9306

器件型号:PCA9306主题中讨论的其他器件: TCA9617B

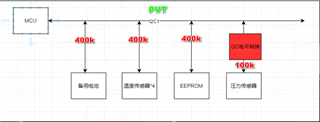

1、I2C 拓扑如下:电池存取率为100k、其他设备存取率为400k、I2C 通信没有问题

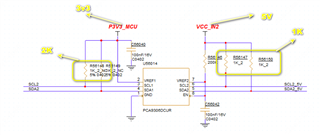

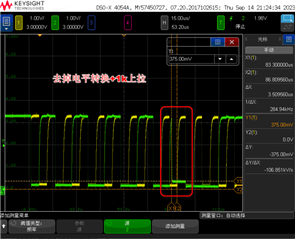

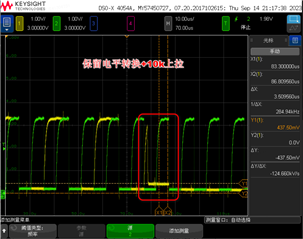

2、在以下 I2C 拓扑中、添加了 PCA9306。 PCA9306的输入上拉电阻为2k、电源为3V3、输出为1k 上拉电阻、电源为5V。 当 I2C 使用100k 来访问电池时、ACK 无法下拉,然而、当其他 I2C 器件访问超过400k 的速率时、没有问题。

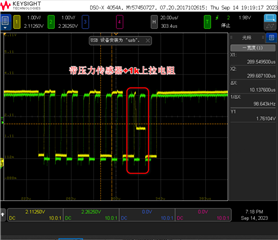

3、将输出的上拉电阻从1k 调整到10k Ω 时、可以降低 I2C 的 ACK

您能解释一下为什么?