您好、TI 工程师!

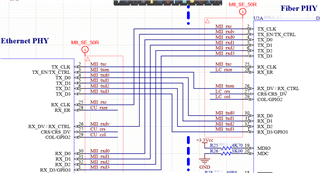

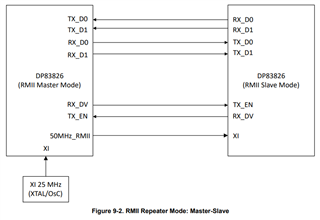

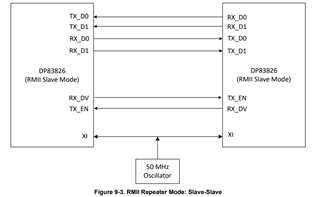

我们有一个以太网卡设计、该设计使用 MII 中配置的2x DP83822IF、以从 PCIe MAC 实现 MDI 铜线到 MDI 光纤介质的转换。

MAC 和系统处理器无法访问 MDIO 寄存器、因此两个 DP83822 PHY 的配置完全通过硬件自举来完成。

我成功实现了@ 100Mbps 的重复链路、希望通过进行无限 ping 测试和监控数据包丢失来验证 MII 链路的稳定性。

每次,我得到大约2-3%的包丢失(在数千,有时是数千个 Ping 的 thens )。

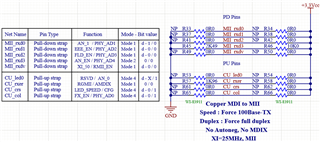

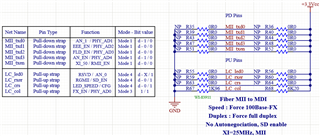

我们的配置如下:

铜缆 PHY

100BASE-TX 全双工、无 MDIX、无自动协商、MII 25MHz、禁用 SD

光纤 PHY

100BASE-FX 全双工、无 MDIX、无自动认证、MII 25MHz、支持 FX、 启用 SD

Copper PHY <-> Fiber PHY MII 介质转换器连接:

TXD[0..3]-> RXD[0..3]

RXD[0..3]<- TXD[0..3]

TX_CLK -> RX_CLK

RX_CLK <- TX_CLK

TX_EN -> RX_DV

RX_DV <- TX_EN

RX_ER、CRS 和 COL 不是两个 PHY 之间的共享连接。

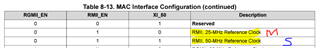

两个 PHY 之间的25MHz 时钟是共享的、可以由一个 CMOS 振荡器对两个 PHY 进行馈送。 它符合 DP83822IF 最低要求的规格(25MHz、±25ppm)。

两种 PHY 的搭接如下、如前所述、工作正常、我们通过信号检测实现一致的链路建立和断开、Windows 中的网络适配器遵循 SD 的状态。

我的问题是、您是否知道我为什么会稳定地丢失2-3%的数据包?

我有第二种设计、它使用相同的 PCIe MAC 到 MDI 铜线、100k+ ping 中的数据包损耗为0%。 我很确定丢包是由于介质转换器造成的。

非常感谢您、您完全可以提供有关此主题的更多信息!