尊敬的 TI 技术团队:

我将在我们的产品中使用 TI 的 SN75DP159 HDMI2.0转接驱动器/重定时器芯片来实现 HDMI2.0发送器接口。 HDMI2.0接口到目前为止工作正常,但不幸的是我们没有通过 HDMI 兼容性测试,我们外包给了外部的测试机构。到目前为止,所有测试都通过了,除了测试 ID H1~4。 该测试将测量每个差分 HMDI TMDS 信号(1xClock + 3xData)上的对内偏斜。 HDMI 规范规定了25ps 的最大对内偏斜、这是一个非常小的值。 我们的外部测试机构的结果暴露了以下对内偏斜:

时钟= 38ps

数据0 = 18ps

数据1 = 17ps

数据2 = 14ps

从这些值可以看出、时钟信号的对内偏斜过大、大约超过25ps 限制13ps。 数据信号不会超过限值、但尽管如此、它们仍接近最大值。 限制为25ps。

我们已经检查了 PCB 布线、可以说 Clock+和 Clock-之间的最大长度差异小于100um (几乎没有差异)。 当我们假设典型信号速度为70ps/10mm 时、在 FR4阻抗匹配的 PCB 中、38ps 相当于大于5mm 的信号长度差异。 因此、100um 的长度差不是导致此问题的原因。

此外、HDMI 接收器不会引入此类较大的对内偏斜。 此外、Allion 还指出、他们已校准测量设置、这意味着他们已补偿 Clock+和 Clock-之间的任何信号运行时差异。

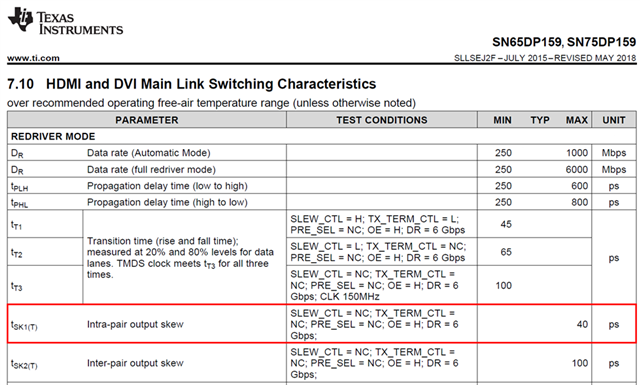

目前、似乎过多的对内偏移是由 SN75DP159引起的。 此处的一个有趣之处是、SN75DP159的数据表显示、线对内最大偏斜可高达40ps!!

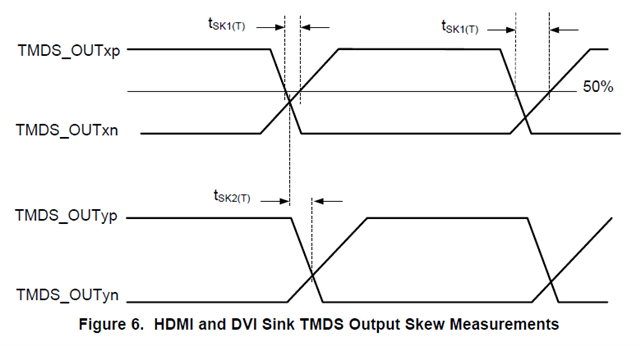

当我参考下图时、对内偏斜被定义为中线交叉点之间的绝对距离:

1Tbit 等于1/6Gbits = 166.666ps。 如果我的回答正确、对内最大偏差不得超过0.15 * 166.666ps = 25ps。

因此、如果我理解正确、DP159的容差(40ps)大于 HDMI 2.0规范(25ps)允许的容差、因此 DP159无法满足 HDMI2.0规范的要求。

你能确认我的想法,还是我错了?

此致

斯特芬