主题中讨论的其他器件:TCAN4550、 RM46L852、

尊敬的团队:

我们遇到了与高温相关的问题。 故障情况和 TCAN4550设置如下:

[问题]

在高温(约60度)下发生多个错误、导致报告的 CAN 通信故障。 故障率约为5%。

在检查中断寄存器(h1050)时、23、24和25位会被置位。

在检查协议状态寄存器(h1044)时、会发现触发位5、6和7 (错误警告、被动错误、总线关闭)。

[电路结构和 TCAN4550设置如下]

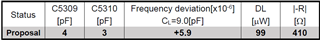

TCAN4550 位定时 设置 :(@40MHz 晶振+-10ppm 容差 /固定500kbps)

BRP= 10 - 1;/ SJW = 1 - 1; TSEG1 = 6 - 1;TSEG2 = 1 - 1;

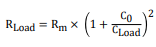

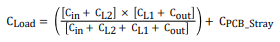

并且、我们已根据 PCB 板上的晶体评估报告检查负载电容值。

[问题]

1.即使我把测试的设置从10TQ 改为80TQ ,缺陷现象仍然是一样的。 我是否也需要对齐 RM46L852的位设置时序?

-

BRP = 1- 1;/ SJW = 10 - 1;/ tseg1 = 69 - 1;/ tseg2 = 10 - 1;

-

正如您在上面的方框图中看到的、两个电路板之间的连接不是长 CAN 电缆、而是大约250mm 的布线。 如果低速时的比特率为500kbps 的任何建议设置、请给出建议。

-

如果除了更改位时间外还有其他改进建议、请告知我。