主题中讨论的其他器件:TFP401A、 TFP401

您好、TI 团队:

您能否说明一下 TFP401A 器件的输出时序参数。

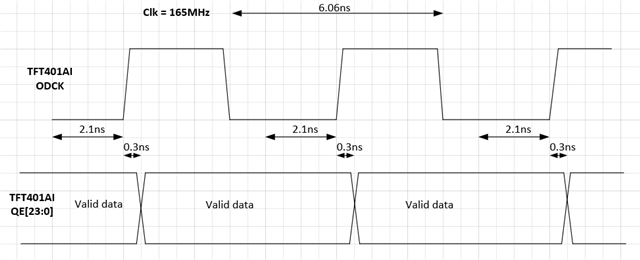

我们在表7.7和图8-4数据表中看到了输出设置和保持时间值。 我们需要将 TFP401器件的输出信号与 LVDS 串行器芯片时序连接。

如果您查看 数据表中的图8-4、则输出时钟"OCK"会相对于数据输出(RGB)进行更改。 我们的问题是、您如何解释输出时序参数的数据表时序值?

您能否说明输出 数据(RGB)何时会相对于 时钟输出 信号发生变化? 如果我们设置"OCK_INV"=高电平、是否需要 在串行器芯片中设置上升沿采样或下降沿采样以满足时序参数?

谢谢!

约翰·约翰逊