请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DP83869HM 主题中讨论的其他器件: LMK00105、 DP83869

您好!

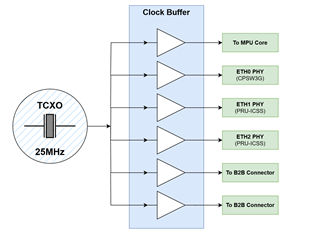

我们正在研发符合 TSN 标准的器件、并且我们拥有3个 DP83869HM、我的问题是哪种方法可以分配25MHz 时钟?

1) 1)使用时钟缓冲器并将时钟分配给全部三个 PHY、或

2) 2)使用以太网 PHY CLK_OUT。 (25MHz 时钟--> PHY1 XI、 PHY1 PHY CLK_OUT --> PHY2 XI、PHY2 PHY CLK_OUT --> PHY3 XI)

此致、

P·帕特尔