您好

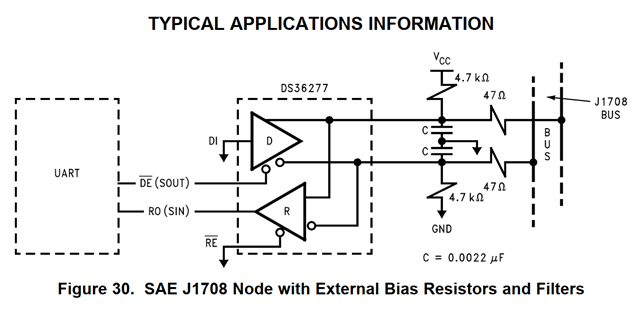

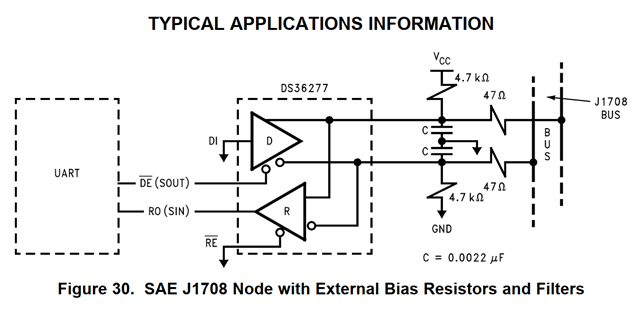

对于 J1708应用、DI 引脚始终接地。

我很好奇如何测量图5? 因为 DI 不能是3V3电平。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

对于 J1708应用、DI 引脚始终接地。

我很好奇如何测量图5? 因为 DI 不能是3V3电平。

PY、您好!

很抱歉耽误你的时间。

虽然 J1708应用确实将 DI 引脚接地、但此器件仍可用于您要通过 DI 引脚发送数据的非 J1708应用。

因此、图5所示情况与 J1708无关-而只是标准的 RS -485。

在 J1708中、从低电平到高电平的传播延迟是禁用驱动器和为外部网络充电的时间。 正常情况下、器件在输出低值的同时禁用时的最大值为11ns (典型值)和60ns (最大值)、但其外部网络的 RC 时间常数要小得多;因此、大部分延迟实际上是由外部系统造成的。

对于高电平到低电平的传播延迟、是从低电平的启用时间+外部电容器的放电时间。 低值的启用时间通常为30ns、但最多为60ns (最大值)-不过、J1708外部网络的电容同样要大得多、因此该规格可以在实际系统中减慢一点。

总之、

1.这仍然是符合 RS 至485的器件。 图5与传统 RS 至485比 J1708更相关、在 J1708设计中可以忽略图5。

2.系统看到的"传播延迟"实际上将是从使能到低电平时间(TPZL)+高电平到低电平传播延迟(TPHL)和从低电平禁用(TPLZ)的外部放电时间+有效低电平到高电平传播延迟的外部充电时间 集成控制器(TPLH)。

此致!

帕克·道德森