主题中讨论的其他部分:鳄鱼夹

我使用 FPGA 写入 PHY 寄存器、就像使用其他 PHY 一样。

我发送32个1作为前导码、后跟:

SOF 0b01

操作码0b01 (用于写入)

PHY ADDR 0b00001 (根据数据表8.5.3)

寄存器 ADDR 0x00 (BMCR)

I 设置位8和13 = 1并且位12 = 0

然后是相同的 SOF/OPCOD/PHYADDR、但 REG ADDR 0x0A、位14 = 1 (用于 FX 启用)

我这样做不成功。

我缺少什么吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我使用 FPGA 写入 PHY 寄存器、就像使用其他 PHY 一样。

我发送32个1作为前导码、后跟:

SOF 0b01

操作码0b01 (用于写入)

PHY ADDR 0b00001 (根据数据表8.5.3)

寄存器 ADDR 0x00 (BMCR)

I 设置位8和13 = 1并且位12 = 0

然后是相同的 SOF/OPCOD/PHYADDR、但 REG ADDR 0x0A、位14 = 1 (用于 FX 启用)

我这样做不成功。

我缺少什么吗?

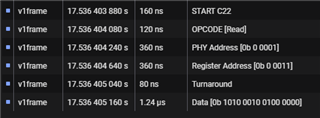

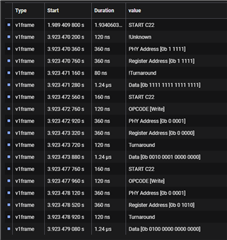

我成功读取寄存器0x3、然后获得了每个数据表的默认值:

我决定在一些导线上焊接到 MDIO 和 MDC。 然后使用我的 SALEAE 分析器。

我们使用另一个 PHY 并成功写入所有类型的设置。 也焊接在一些导线上。

观察分析器上针对 TI PHY 的情况(如所述)、写入命令和寻址看起来是正确的。

顶部的混乱似乎是前导码- SALEAE MDIO 解码器必须解决这个问题。 另一个 PHY 表现相同。

我不确定 TI PHY 为什么不会初始化-我一定遗漏了一些内容。

尊敬的 Craig:

如果在有效载荷区域内、则此时 PHY 应该控制线路并取出其寄存器值。 不过、该行为表示其他因素可能干扰了此操作;无论是 SoC 未能释放线路、还是其他因素。 从理论上讲、这一行应该是开漏行、因此 PHY 的任务是仅在出现"0"时按住该行、然后在出现"1"时释放。

可能有理由认为写入命令正在执行、但读取时的干扰正在将该"1"伪装成"0"、反之亦然、从而在回读时对 SoC 造成干扰。

我想确认 SoC 不会干扰此操作。

此致、

格罗姆

您好、Gerome、

我已经得出结论,这是我的 Verilog 的问题。 我无意中将 MDIO 线路设置为仅输出、而将 INOUT 设置为双向。

我现在能够有信心地回读我的写作。 我现在看到的是、回读寄存器0x0包含用于 IEEE 断电的位11高电平。 我没有设置该位。 这是否可以解释为什么我没有看到任何迹象表明 PHY 处于活动状态。 我将使用两个指示来确定 PHY 是否处于活动状态。 1) 1) RX 和 TX 时钟如 Chipscope 中所示移动(还应该查看 RX 数据) 2)收发器上的 LED 亮起。

尊敬的 Craig:

EVM 将此位读取为"0"、但当此引脚动态变为低电平状态后、此位也会为"1"。 我还希望检查此引脚是否意外通过引脚设置为低电平。 这将需要快速检查万用表。 我确实注意到、没有为该线路填充 PU;只有一个 PD、因此 SoC 需要驱动该线路以确保其为高电平。

如果您要手动将此位设置为"0"、回读会保持吗?

示波器中的 SMI 波形看起来是什么样子?

当您的意思是您使用 PHY 启动或不启动的两个指示时、您是否看不到 RX_CLK 切换?

此致、

格罗姆