主题中讨论的其他器件: MAX3243E

尊敬的团队:

请参阅附件、 "UBS-240_MAX3221E Schematic Review.pdf" 。

您能帮助提供评论吗? 非常感谢。

e2e.ti.com/.../UBS_2D00_240_5F00_MAX3221E-Schematic-Review.pdf

非常感谢。

吉米

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的团队:

请参阅附件、 "UBS-240_MAX3221E Schematic Review.pdf" 。

您能帮助提供评论吗? 非常感谢。

e2e.ti.com/.../UBS_2D00_240_5F00_MAX3221E-Schematic-Review.pdf

非常感谢。

吉米

尊敬的 Jimmy:

请注意、如果 VDD = 3.3V、则我不会看到任何问题。

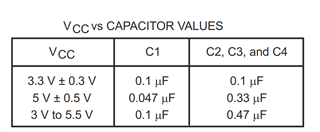

但是、如果 VDD =/= 3.3V、请参阅下表:

Clemen 也是正确的-在可以实现单芯片解决方案时、MAX3243E 也可以满足类似的设计目标、而无需使用3个 IC。 对于 MAX3243E 上未使用的接收器端口(RIN)-您可以将其上拉至 VCC (只要未使用的 RIN 到 VCC 的唯一连接) 由于0V 电平会将器件状态置于保护状态、因此将 Rin 引脚拉至 VCC 会保持有效电平、并且您可以将未使用的 ROUT 保持悬空状态。

如果您有任何其他问题、敬请告知!

此致!

帕克·道德森。

从技术角度而言、RS -232标准0V 未定义;逻辑零在3V 至15V 范围内有效、逻辑1在-3V 至-15V 范围内有效。

如果您使 Rin 输入保持悬空-当它在内部下拉时、这样 ROUT 电平将保持恒定、因为该器件不符合标准接收器灵敏度- 信号无效、/INVALID 输出将在整个运行期间被强制为低电平-即使 也可以与其他器件通信。

这限制了器件的可用性、因为该设计选择破坏了主要功能-如果您将未使用的 Rin 输入连接到 VCC、这将不再成为问题、因为未使用的通道会看到"有效"的数据。

所以、您可以将 Rin 保持悬空、但这样做会降低器件的功能和灵活性(要为不使用的功能付费、但仍要为其付费)。 因此、对于通用系统来说、说直接保持"RIN"悬空是 不明智 的-因为该假设并不适用于所有情况、而在逻辑上将未使用的 VIT 至少拉至 RIN+(max)可以使器件更灵活、因为在此设置中不会阻止器件的实际功能。

帕克·道德森